# Formation of Molecular-Scale Gold Nanogap Junctions via Controlled Electromigration

G. Esen, S.A. Getty, M.S. Fuhrer

Department of Physics and Center for Superconductivity Research, University of Maryland, College Park, MD 20742-4111, USA

**Abstract**. We have used a feedback method to control the electromigration of gold nanowires to form nanogap junctions, similar to recent reports [1, 2]. We have studied gold wires fabricated with conventional electron-beam and photolithography on thick  $SiO_2$  and thin  $Al_2O_3$  (over Al) substrates. We find that the role of feedback mechanism is to control the local temperature of the electromigrating nanowire, and controlled breaking of nanowires is possible only when the wire is in good thermal contact to either the substrate or the bulk metal leads.

#### INTRODUCTION

Electromigration (EM) is the electrical current-induced diffusion of atoms in a thin metal film, and is important as a serious mode of failure in integrated circuit interconnects in the semiconductor industry [3]. Failure of a narrow wire due to EM has been utilized extensively to prepare stable electrical contacts for single-molecule experiments [4] which rely on preparing a nanogap in the size of the molecule whose conductance properties are being measured. Although this technique is used extensively, the mechanism behind the formation of the nanogaps and how it depends on metal/substrate interaction is not well understood. When increasing current in a wire, two processes drive EM: the electric field increases linearly with the current, and the temperature increases due to Joule heating. The rate of electromigration depends on both the electric field and the temperature, depending on electric field as a power law, and temperature exponentially (since electromigration is electric field-biased motion of thermally-activated atoms). In order to properly design wires for electromigration to form nanogaps, it is important to understand whether the temperature or electric field dominates the EM process.

## **EXPERIMENTAL**

For single-molecule experiments, it is advantageous to have a third gate electrode nearby the gap junction. This has been accomplished previously in two different configurations; in the first configuration the EM junctions are fabricated on top of thick (100-500 nm) SiO<sub>2</sub> gate dielectric over the degenerately-doped Si [4] gate, whereas in the second configuration the junctions are fabricated on a local gate

consisting of a narrow Al wire with the thin (3-10 nm) native Al<sub>2</sub>O<sub>3</sub> as gate dielectric [5].

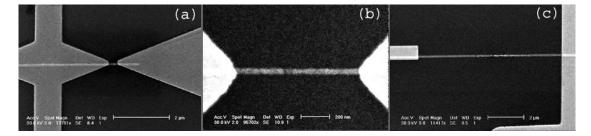

**FIGURE 1.** SEM microgrographs of the three different device geometries. Part (a) shows a short Au wire on SiO<sub>2</sub> substrate where the wire is 325 nm long, 80 nm wide and 30 nm thick. Part (b) shows an Au wire on Al<sub>2</sub>O<sub>3</sub> (over Al) substrate where the wire is 900 nm long, 40 nm wide and 15 nm thick. Part (c) shows a long gold wire on SiO<sub>2</sub> substrate where the wire is 8 micrometers long, 100 nm wide and 30 nm thick. In both parts (a) and (c) the scale bar is 2 micrometers whereas in part (b) the scale bar is 200 nm.

We have fabricated and studied electromigration in three different device geometries using these two configurations, in order to vary the thermal coupling to the substrate and/or the bulk metal leads (see Figure 1): (a) Short Au wire on SiO<sub>2</sub> (over Si) substrate (good thermal coupling to the bulk metal leads), (b) Au wire on Al<sub>2</sub>O<sub>3</sub> (over Al) substrate where due to thin Al<sub>2</sub>O<sub>3</sub> oxide layer and high thermal conductivity of the Al this geometry has good thermal coupling to the substrate, and (c) long Au wire on SiO<sub>2</sub> (over Si) substrate (poor thermal coupling of the Au wire to the bulk metal leads and substrate). We expect that the thermal conductance of the center of the wire to the substrate is greatest in (a) and least in (c) (we roughly estimate the thermal conductance along the wire in (b) as comparable to that through the Au/Al<sub>2</sub>O<sub>3</sub> interface; hence (a) has the greatest thermal conductance because of its geometry).

In fabrication of our devices we did not use a wetting layer for the gold deposition. To control the electromigration process we used a computer-controlled feedback scheme similar to ref. 2, consisting of the following steps: We first measure a reference conductance value than we increase the voltage until the conductance drops by typically 2 to 5 percent from the reference conductance value. When we observe such a conductance drop we decrease the voltage and measure the new reference conductance value. We repeat this process until the desired conductance is reached. Experiments were performed in a gas flow <sup>4</sup>He cryostat at substrate temperatures from 1.3 K to room temperature (RT).

#### RESULTS AND DISCUSSION

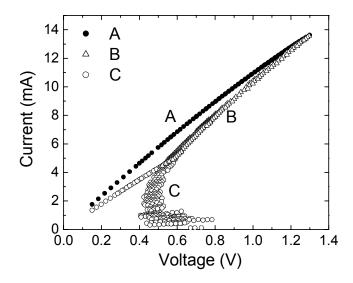

A representative current vs. voltage  $(I-V_{\rm bias})$  curve taken through a feedback controlled electromigrating process for a short Au wire in SiO<sub>2</sub>/Si [geometry (a)] is shown in Figure 2 below. The data labeled A show a smooth I vs.  $V_{\rm bias}$  curve indicating that electromigration has not begun in the gold wire. Although there is a resistance increase with increasing bias in A, we found that if we stop the voltage bias

before the wire begins to lose material due to electromigration, this resistance increase is reversible. Such a reversible resistance increase shows that the gold wire heats up before electromigration begins. The data labeled B show that after this initial heating the gold wire begins to lose material due to EM and its resistance increases irreversibly. The data labeled C show that one can stop and restart the voltage bias before the gold wire totally fails. I-V<sub>bias</sub> curves of two bias processes perfectly match each other indicating that in the second biasing process the gold wire first heats up to the temperature where significant electromigration process takes place, and restarts to dissipate material.

**FIGURE 2.** Current vs. bias Voltage curve of a feedback controlled electromigration process of an Au wire that has geometry (a) of Figure 1 at T=1.3 K. Part A is a smooth curve indicating than the EM has not begun whereas in part B the resistance of the line increases irreversibly due to EM. Both parts A and B are recorded in a single voltage biasing process, producing a final resistance of ~120  $\Omega$ . At this point the voltage was reduced to zero for some time. When the bias process was restarted in C, the wire resistance is the same, demonstrating that the EM process may be frozen by turning off the voltage.

We achieved this kind of feedback-controlled electromigration behavior only in device geometries (a) and (b), i.e. short Au wire on SiO<sub>2</sub>/Si and Au wire on Al<sub>2</sub>O<sub>3</sub>/Al. We could not achieve same kind of controllability with geometry (c), a long Au wire over SiO<sub>2</sub>/Si substrate. Although we observed that feedback control of electromigration requires good thermal heat-sinking of wires either to the substrate or to the bulk of the leads (Such as device geometries (a) and (b) in Figure 1), we did not observe any dependence on the temperature of the environment. Feedback control of electromigration was possible from 1.3 K to RT. Poorly heat-sunk wires failed abruptly, leading to large gaps (greater than 5 nm, as measured by SEM) which had immeasurably small conductance.

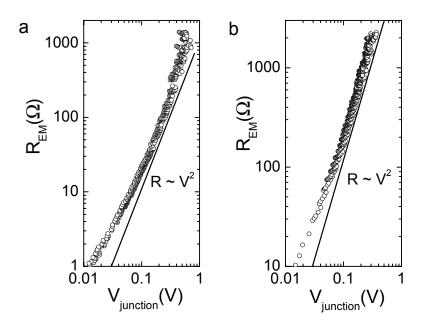

We calculated the resistance increase due to electromigration by modeling it as a serial resistor with the leads where the resistance due to electromigration,  $R_{\rm EM}$ , is changing with applied bias as the wire electromigrates. Figure 3 shows the voltage drop at the junction,  $V_{\rm junction}$ , after the voltage drop at the leads subtracted from the

applied bias voltage vs.  $R_{\rm EM}$  for two devices on which we performed feedback-controlled electromigration. The solid lines in both Figure 3a and 3b indicate slopes with  $R_{\rm EM}$  proportional to  $V_{\rm junction}^2$ . In our devices the increase of the resistance due to electromigration is proportional to  $V_{\rm junction}^n$  where  $n=2\pm0.5$  indicating roughly constant power dissipation during electromigration. It can also be seen that the power is greater in (a) than in (b), as expected considering the greater thermal conductance of the wire in (a). If the EM process were primarily bias-controlled, we would expect that  $V_{\rm junction}$  would be roughly constant, which is certainly not the case; the electromigration process occurs over nearly two orders of magnitude of  $V_{\rm junction}$ .

In conclusion we were able to perform feedback controlled electromigration in gold wires with good thermal heat sinking over a temperature range from 1.3 K to RT in a gas flow  $^4$ He cryostat. We observed that current-voltage relationship when EM occurs is roughly  $I \sim V_{\rm junction}^2$ , indicating roughly constant temperature during EM and the EM process is temperature-controlled rather than bias-controlled.

This work was supported by the U.S. DOE under grant DOE-FG02-01ER45939, and the DCI Postdoctoral Fellowship Program.

**FIGURE 3.** Voltage drop at the junction vs. the resistance increase of the junction due to electromigration,  $R_{\rm EM}$ . (a) shows  $R_{\rm EM}$  vs.  $V_{\rm junction}$  for geometry (a), short Au wire on SiO<sub>2</sub> substrate, whereas (b) shows  $R_{\rm EM}$  vs.  $V_{\rm junction}$  for geometry (b), Au wire on Al<sub>2</sub>O<sub>3</sub> substrate. Solid lines show the slope for  $R_{\rm EM}$  proportional to  $V_{\rm junction}^2$ .

## REFERENCES

- 1. Houck et.al., cond-mat/0410752 v1.

- 2. D. R. Strachan, et al., Appl. Phys. Lett. 86, 043109 (2005).

- 3 J. R. Lloyd, Semicond. Sci. Technol. 12, 1177-1185 (1997), and the references therein.

- 4. H. Park et al., Appl. Phys. Letters 75, 301-303 (1999).

- 5. W. Liang et al., Nature 417, 725-729 (2002).