A Thinking Person's Guide to Programmable Logic

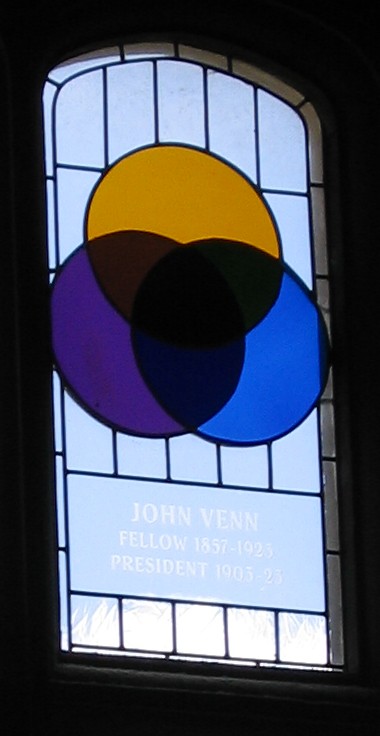

The basic algebra of binary elements is called Boolean Algebra. As noted in Wikipedia, it is named for George Boole (1815-1864), an English mathematician pioneer in logic. His book "The Laws of Thought" (1854) lays out the algebra of thought, or reasoning.

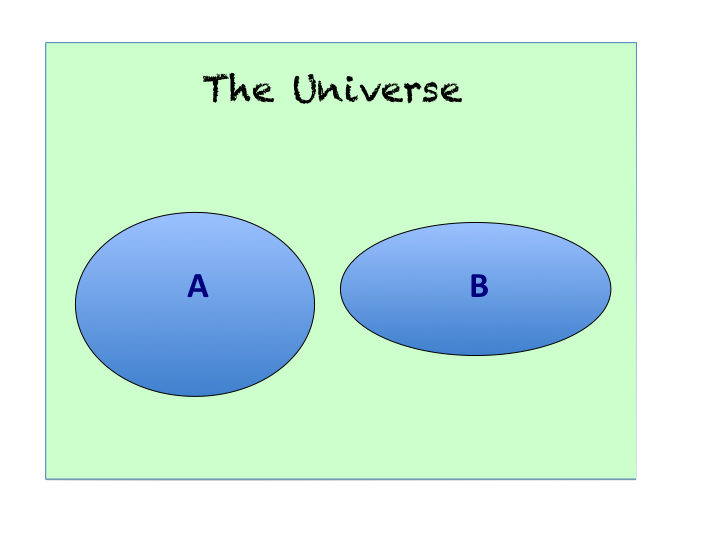

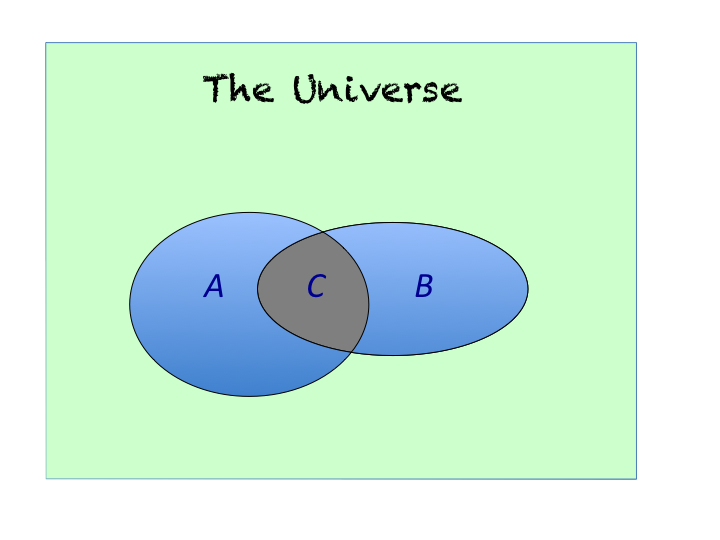

Before getting into the details of Boolean algebra, we can first

consider a more general visual description of sets and set theory,

and how elements and sets are related. To begin, consider the

following depiction of the "Universe":

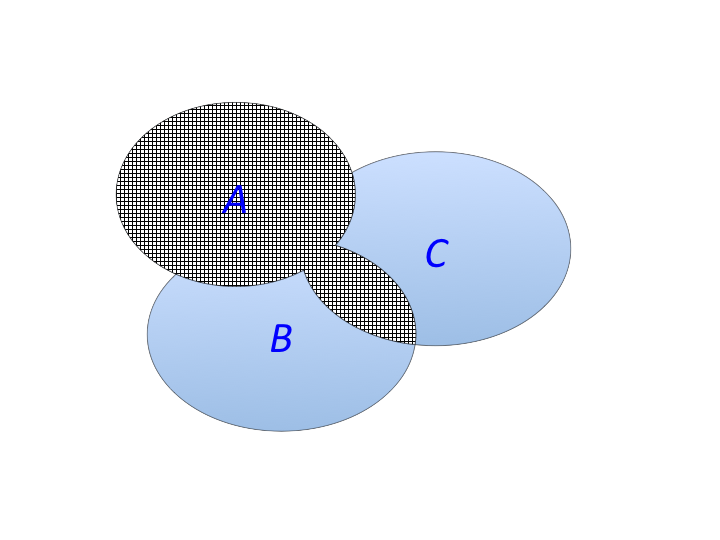

So we can write $C=A$ and $B$, or more concisely $C=A\&B$ (and sometimes you will see $C=A\cdot B$), or in the jargon of set theory, $C=A\cap B$, where the symbole $\cap$ means "intersection".

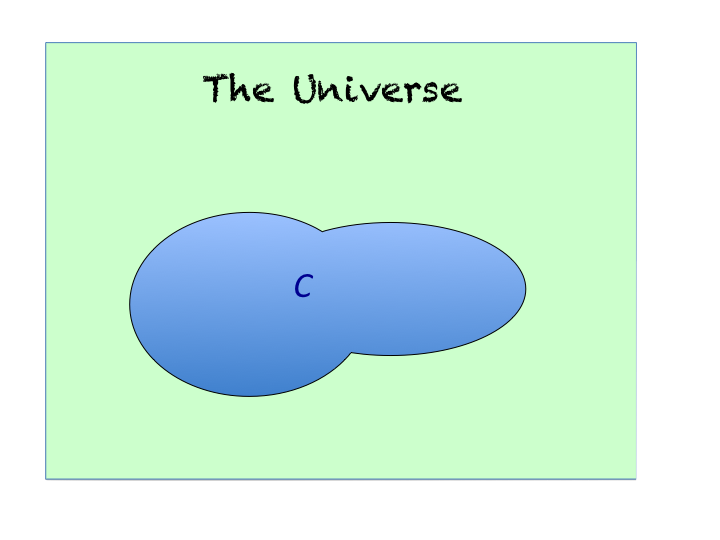

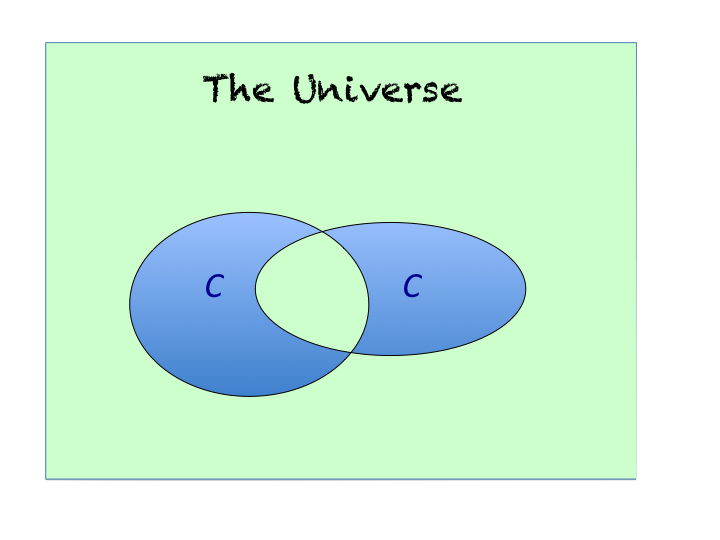

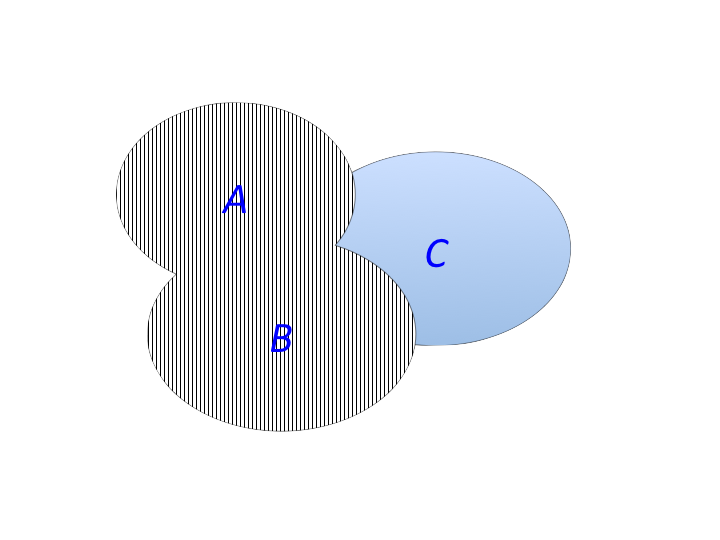

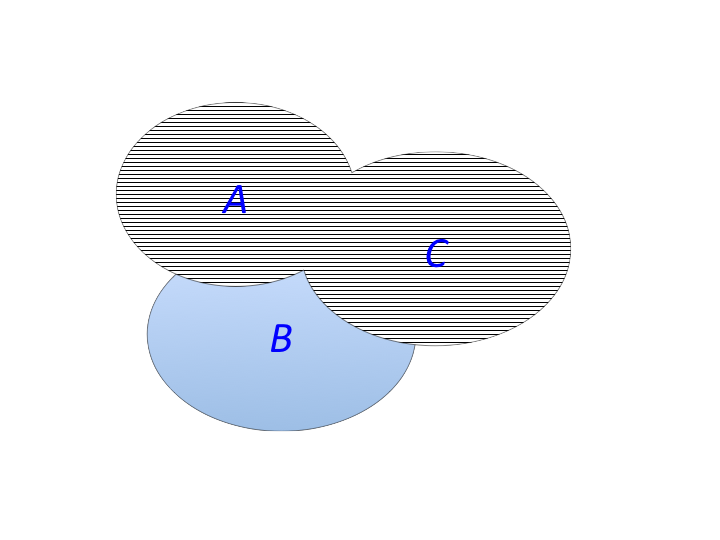

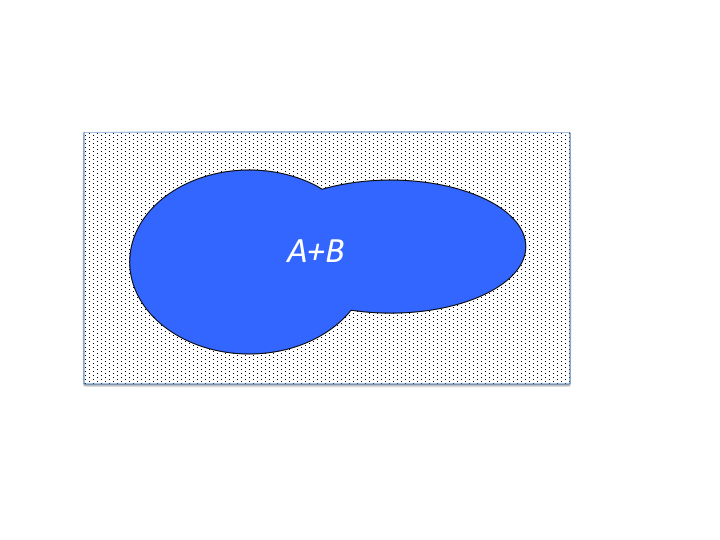

One can also form the "union", or in other words $C=A$ or $B$,

or more commonly $C=A+B$, $C=A|B$, $C=A\cup B$:

| and | or | xor |

|---|---|---|

| $A\cdot B$ | $A+B$ | $A\oplus B$ |

Brief Excursion to Bayesian Statistics | Back to top |

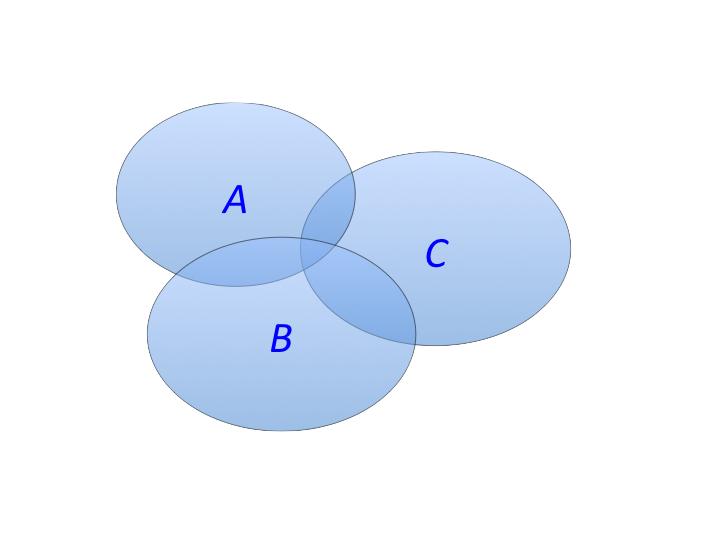

The area $C$ is the intersection of $A$ and $B$, can be written as $A\cap B$, and can be thought of in 2 ways, relative to the areas of $A$ and $B$:

$$P(B|A)\cdot A=P(A|B)\cdot B$$

And if we divide both sides by $U$, and use $P(A)=A/U$ and $P(B)=B/U$ we get the equation: $$\frac{P(B|A)}{P(B)}=\frac{P(A|B)}{P(A)}$$ This famous equation is called Bayes' Theorem, first described by Rev. Thomas Bayes (1701-1761) and updated by Pierre-Simon Laplace in 1812. It describes a way of understanding statistical probabilities given prior information, and is extremely important in many fields of science that heavily rely on statistics. As usual, the article in Wikipedia is quite good and worth reading. Back to top

Boolean Algebra | Back to top |

| and |

| = |  |

| ($A\cdot B) + (B\cdot C)\cdot (B+C)$ | $=$ | $(A\cdot B) + (B\cdot C)\cdot B + (B\cdot C)\cdot C$ |

| $=$ | $(A\cdot B)+(B\cdot C)+(B\cdot C)$ | |

| $=$ | $(A\cdot B)+(B\cdot C)$ | |

| $=$ | $(B\cdot A)+(B\cdot C)$ | |

| $=$ | $B\cdot (A+C)$ |

The Digital World | Back to top |

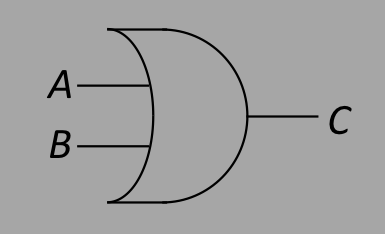

| and: $C=A\cdot B$ | or: $C=A+ B$ | xor: $C=A\oplus B$ | not: $C=\bar A$ |

|

|

|

|

| $A$ | $B$ | $A\cdot B$ | $A+B$ | $A\oplus B$ | $\bar A$ | |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 | 0 | 0 |

The truth table for showing the validity of the distributive property, given for example $A\cdot (B+C)=(A\cdot B)+(A\cdot C)$ would be:

| $A$ | $B$ | $C$ | $B+C$ | $A\cdot(B+C)$ | $A\cdot B$ | $A\cdot C$ | $(A\cdot B)+(A\cdot C)$ | ||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | ||

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | ||

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | ||

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

You can see in the above truth table that the distributive property holds up.

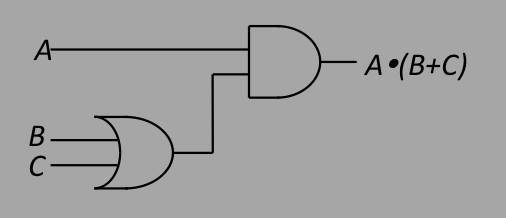

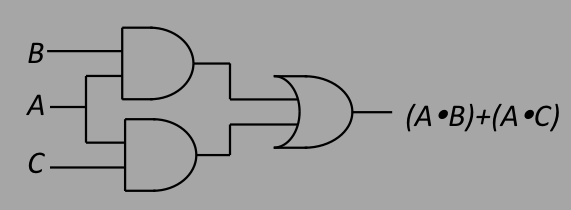

To see the utility of the distributive property, let's form the "network" of gates that implements $A\cdot (B+C)$ and $(A\cdot B)+(A\cdot C)$. First, $A\cdot (B+C)$:

Next, $(A\cdot B)+(A\cdot C)$

Clearly, the former might be preferred as it uses fewer gates. Back to top

Boolean Properties of Gates | Back to top |

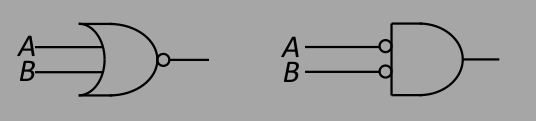

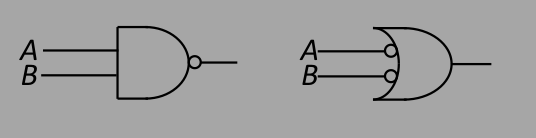

Stated in the language of logic gates, this example above says that if you take a gate and change the OR's into And's' and invert all of the inputs and outputs, you get the same logic result. This also works for the case: $$\overline{AB}=\bar A + \bar B$$ which has the following circuit equivalence:

but in plain English:

We can use DeMorgan's laws to simplify many circuits. For instance, consider the $XOR$ circuit $A\oplus B$. This circuit says "A or B but not both", which means

$A\oplus B=(A+B)\overline{AB}$

We can simplify $\overline{AB}=\bar{A}+\bar{B}$ to get

$A\oplus B=(A+B)(\bar{A}+\bar{B})$

Now we use the distributive propery and write the above as

$A\oplus B=(A+B)(\bar{A}+\bar{B})=A\bar{A}+A\bar{B}+B\bar{A}+B\bar{B}= A\bar{B}+B\bar{A}$

or $$A\oplus B=A\bar{B}+B\bar{A}$$ We can also investigate

$$\overline{A\oplus B}=\overline{A\bar B+B\bar A}= (\overline{A\bar B})(\overline{B\bar A})=(\bar A+B)(A+\bar B) =\bar{A}A+BA+\bar{A}\bar{B}+B\bar{B} =AB+\bar{A}\bar{B}\label{xorbar}$$

which means we can write $$\overline{A\oplus B}=A\oplus\bar{B}=\bar{A}\oplus B$$

Does something like $C+(A\oplus B)$ distribute to $(C+A)\oplus(C+B)$? When you work out the logic using DeMorgan's theorem, you will find that it does not.

DeMorgan's law turns out to be very useful in the world of programmable logic in that it can help a great deal in simplying logic circuits, and as you will see, when we build circuits out of the high level programmable logic language, simplification in the "compilation" can be important especially in FPGAs that have limited numbers of gates (see below). Back to top

Networks of Gates | Back to top |

To begin, let's be slightly formal and define a 2-input function $F(x,y)$ as representing the following truth table:

| x | y | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$F$ is "true" (1) when $x$ and $y$ are the same (both false, 0, or both true, 1)

otherwise $F$ is "false" (0). (Let's use 0 and 1 from now on to make it simpler.)

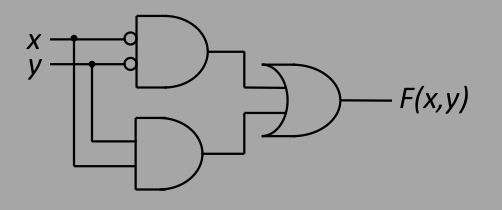

This tells us how to construct the network: combine the terms $x$ and $y$ such that

$F$ is 1. In this example, we can see easily that $F(x,y)=\bar x\bar y + xy$.

Each "miniterm" (here $\bar x\bar y$ and $xy$) is a product ("and")

and you "sum" the products to find where the function is "true" (1), hence we call

this technique the "sum of products", or "SOP" for shorthand. The following diagram

shows the gate network that maps to $F(x,y)$:

| x | y | z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

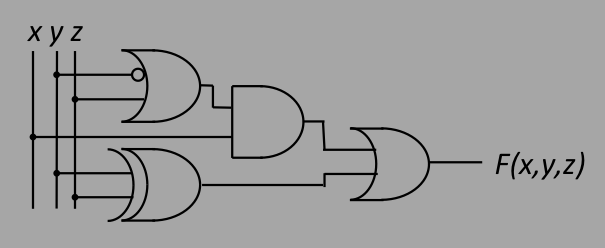

The miniterms are constructed from where $F=1$, which means the rows where $xyz=001$ ($\bar x\bar y z$), $010$ ($\bar x y \bar z$), $011$ ($\bar x yz$), and $101$ ($x\bar y z$). The SOP is therefore:

$F(x,y,z)= \bar x\bar y z + \bar x y \bar z + \bar x yz + x\bar y z$

This can be simplified by using the above rules for Boolean logic:

| $F(x,y,z)$ | $=$ | $\bar x\bar y z + \bar x y \bar z + \bar x yz + x\bar y z$ |

| $=$ | $(\bar x+x)\bar y z + (\bar z+z)\bar x y$ | |

| $=$ | $\bar y z + \bar x y$ |

where we have used the fact that $\bar x+x=1$ and $\bar z+z=1$. The gate network is

shown next:

$F(x,y)=\bar x\bar y+xy = \overline{x+y}+\overline{\bar x+\bar y} =\overline{(x+y)(\bar x+\bar y)}$

Note that we can invert $F$ and simplify to get

$\bar F(x,y)=(x+y)(\bar x+\bar y)=x\bar x+y\bar x+x\bar y+y\bar y =\bar y x+\bar x y$

Notice that $\bar xy+\bar yx$ are the two terms where $F(x,y)=0$, which is a new way to construct networks: form the product of sums where $F=0$. So we have gone from representing where $F=1$ by a sum of products to a product of sums (POS). It turns out that either SOP or POS works, and whether you one or the other may depend on details of the network. Most people think that the rule of thumb is to use the one with the fewest "miniterms": use SOP if the number of terms where $F=1$ is less than where $F=0$, or use POS if the other way around. And of course, always simplify afterwards! The following is an example of where a POS works well:

| x | y | z | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

We can write down $F(x,y,z)$ using the product of sums (POS, $F=0$) and simplify:

| $F(x,y,z)$ | $=$ | $(\bar x+\bar y+z)(x+\bar y+\bar z) (x+y+z)$ |

| $=$ | $(\bar x+\bar y+z)[xx+xy+xz+\bar yx+\bar yy+\bar yz+\bar zx+ \bar zy+\bar zz]$ | |

| $=$ | $(\bar x+\bar y+z)[x+xy+xz+\bar yx+\bar yz+\bar zx+\bar zy]$ | |

| $=$ | $(\bar x+\bar y+z)[x+x(y+\bar y)+x(z+\bar z)+\bar yz+\bar zy]$ | |

| $=$ | $(\bar x+\bar y+z)[x+\bar yz+\bar zy]$ | |

| $=$ | $\bar xx+\bar x(y\oplus z)+\bar yx+\bar y\bar yz+\bar y\bar zy+ zx+z\bar yz+z\bar zy$ | |

| $=$ | $\bar x(y\oplus z)+x(\bar y+z)+(y\oplus z)$ | |

| $=$ | $x(\bar y+z)+(y\oplus z)$ |

with the following network of gates:

There are various other methods that people have employed in the past for going from a truth table to a network of gates. For instance, Karnough maps is another method of going from truth tables to gates (see the article in Wikipedia. It does not add enough to warrant more here, but suffice it to say that all of these techniques will be useful by the software that eventually builds the code that runs in programmable logic devices such as FPGAs. Back to top

Binary, Octal, Decimal, Hexadecimal | Back to top |

To set the context, a regular every-day decimal number is written in base 10, and the digits tell you how many of that power of 10. For instance, the number $3282_{10} = 2\times 10^0 + 8\times 10^1 + 2\times 10^2 + 3\times 10^3$. To convert to base 2, we will need to know how to represent $3282_{10}$ in terms of the amount of $2^0$, $2^1$, $2^2$, and so on. So it is worth memorizing (don't worry about it, if you use enough programmable logic you will end up remembering this by heart) the various powers of 2:

| $n$ | $2^n$ | |

|---|---|---|

| $0$ | 1 | |

| $1$ | 2 | |

| $2$ | 4 | |

| $3$ | 8 | |

| $4$ | 16 | |

| $5$ | 32 | |

| $6$ | 64 | |

| $7$ | 128 | |

| $8$ | 256 | |

| $9$ | 512 | |

| $10$ | 1024 | |

| $11$ | 2048 | |

| $12$ | 4096 | |

| $16$ | 65536 |

This is kind of klunky, but a computer algorithm can do this easily. Here's the trick: the using the least significant bit (LSB) of the resulting binary number will be determined by whether the decimal number to convert is odd or even. So if you divide it by $2$, then the remainder will be the LSB of the target binary number. Then you take the result of $3282/2$, and whether that is odd or even will determine the next bit of the target binary number, and so on. So the following outlines the calculation using division and remainder:

| $3282/2$ | = | $1641$ | remainder | $0$ |

| $1641/2$ | = | $820$ | remainder | $1$ |

| $820/2$ | = | $410$ | remainder | $0$ |

| $410/2$ | = | $205$ | remainder | $0$ |

| $205/2$ | = | $102$ | remainder | $1$ |

| $102/2$ | = | $51$ | remainder | $0$ |

| $51/2$ | = | $25$ | remainder | $1$ |

| $25/2$ | = | $23$ | remainder | $1$ |

| $12/2$ | = | $6$ | remainder | $0$ |

| $6/2$ | = | $3$ | remainder | $1$ |

| $3/2$ | = | $1$ | remainder | $1$ |

| $1/2$ | = | $0$ | remainder | $1$ |

Then you read off the binary number with the most significant bit (MSB) from the bottom of the above stack, and the LSB at the top: $3282_{10}=111011010010_2$.

Octal representations are in base 8, which means you only need 8 digits: $0-7$. The largest digit will be a 7, and that can be represented by the binary number $111$ since $7=4+2+1$ and the 3 digits tell us how many $4$, $2$, and $1$'s are in the number. Similarly, $6=110$, $5=101$, $4=100$, $3=011$, $2=010$, and $1=001$. Since 8 is a power of 2, there's a nice trick on how to go between binary and octal. For instance, let's take $110011010010_2$ and convert to octal by grouping 3 successive bits in a row like this: $110,011,010,010_2$. We can then read off the octal representation of the sets of 3: $110=6$, $011=3$, and $010=2$, so we get $110,011,010,010_2=6322_8$.

Hexadecimal is just as easy. Base 16 means we will need 16 digits, so traditionally we use $0-9,A,B,C,D,E,F$. The following table shows the hexadecimal, decimal, and binary representation for the digits:

| Hex Digit | Decimal | Binary |

|---|---|---|

| 0 | 0 | 0000 |

| 1 | 1 | 0001 |

| 2 | 2 | 0010 |

| 3 | 3 | 0011 |

| 4 | 4 | 0100 |

| 5 | 5 | 0101 |

| 6 | 6 | 0110 |

| 7 | 7 | 0111 |

| 8 | 8 | 1000 |

| 9 | 9 | 1001 |

| A | 10 | 1010 |

| B | 11 | 1011 |

| C | 12 | 1100 |

| D | 13 | 1101 |

| E | 14 | 1110 |

| F | 15 | 1111 |

To convert a binary number to hexadecimal, we use the same prescription as for octal but group in units of 4 and read off. For instance, $110011010010_2$ is written as $1100,1101,0010_2$, so the hex representation will be given by $CD2_{16}$. Back to top

Integers in Binary Form | Back to top |

However, this assumes all positive integers. What about negative numbers? One possibility would be to use the MSB for the sign, and the rest of the bits for the magnitude, and below there are several ways to do this. This will of course limit the largest absolute value we can represent, however there's no getting around it, we need to someone convey the sign information.

The simplest way is to just assign the MSB to the sign and use the remaining $n-1$ bits to magnitude. For example, the binary number $1000,0001=81_{16}=129_{10}$ as an unsigned number. If you assign the MSB to the sign, then this becomes $-1_{10}$. A small problem, however, occurs when considering that $1000,0000$ and $0000,0000$ seem to represent the same integer (since $-0=0$). This is not such a big deal but it's ugly and wastes precision (slightly). It is also difficult for machines to deal with (more below).

Another possibility is to use what is called the "1's complement" method. Here we complement (invert) the botton $n-1$ bits when the MSB=1. So to construct the 8-bit binary number for $-1$, you start with the bottom $7$ bits for 1, $000,0001$, complement it to $111,1110$ and add the MSB=1 to get $1111,1110$. This turns out to be better as far as integer arithmetic by machines go, however it still wastes precision since we still have the problem that $1111,1111$ and $0000,0000$ both represent $0=-0$.

A third possibility is called "2's complement". This is the same as the "1's complement" but you add a 1 at the end. So for instance, the 8-bit number $-1$ is constructed by taking the 1's complement of the 7-bit number 1 ($111,1110$), adding 1 ($111,1111$, and setting the MSB (8th bit) to get $1111,1111$. To go from binary to hex, if the MSB is set you subtract 1 and take the 1's complement. For instance, $1011,0101$ is a negative 7-bit number $011,0101$ which is the 1's complement of $100,1010$ which is $4A_{16}=74_{10}$, so $1011,0101=-74_{10}$. In this method, $0$ has a single representation ($0000,0000$), and machines can take advantage of the fact that addition and subtraction works the same on 1's complement numbers.

The following table summarizes the various techniques for a 4-bit number.

| Hex | Binary | MSB | 1's | 2's |

|---|---|---|---|---|

| $0$ | $0000$ | $0$ | $0$ | $0$ |

| $1$ | $0001$ | $1$ | $1$ | $1$ |

| $2$ | $0010$ | $2$ | $2$ | $2$ |

| $3$ | $0011$ | $3$ | $3$ | $3$ |

| $4$ | $0100$ | $4$ | $4$ | $4$ |

| $5$ | $0101$ | $5$ | $5$ | $5$ |

| $6$ | $0110$ | $6$ | $6$ | $6$ |

| $7$ | $0111$ | $7$ | $7$ | $7$ |

| $8$ | $1000$ | $-0$ | $-7$ | $-8$ |

| $9$ | $1001$ | $-1$ | $-6$ | $-7$ |

| $A$ | $1010$ | $-2$ | $-5$ | $-6$ |

| $B$ | $1011$ | $-3$ | $-4$ | $-5$ |

| $C$ | $1100$ | $-4$ | $-3$ | $-4$ |

| $D$ | $1101$ | $-5$ | $-2$ | $-3$ |

| $E$ | $1110$ | $-6$ | $-1$ | $-2$ |

| $F$ | $1111$ | $-7$ | $-0$ | $-1$ |

Computer Arithmetic | Back to top |

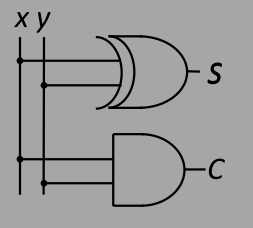

Let $x$ and $y$ be 1-bit numbers, and add them to form $S=x+y$. Best to look at the truth table:

| $x$ | $y$ | $S$ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 2 |

| $x$ | $y$ | $S$ | $C$ |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

The above truth table describes a "1-bit adder". The SOP yields the equations $S=\bar xy + x\bar y = x\oplus y$ and $C=xy$. The gate network is shown below.

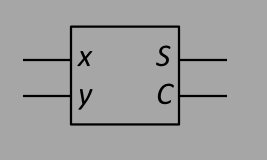

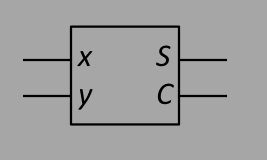

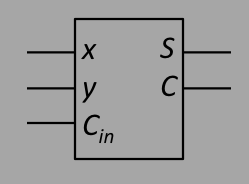

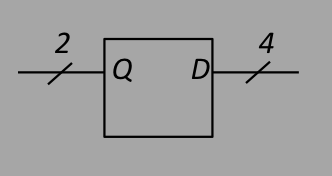

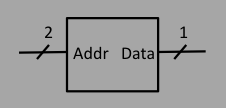

When building complicated circuits, we often take things like 1-bit adders and draw them as "black box circuits". This is in the same spirit as drawing the figure of the $AND$ gate instead of the transistors that make up the gate. For the 1-bit adder, the "primitive" might look something like this:

Note that each of the inputs $x$ and $y$ are 1 bit (1 line) and each of the outputs $S$ and $C$ are also 1 bit (1 line). This will change when we draw primitives of more complex circuits.

| $S1$ | $=$ | $\bar xy\bar C_{in} + x\bar y\bar C_{in} + \bar x\bar y C_{in} +xyC_{in}$ |

| $=$ | $(\bar xy + x\bar y)\bar C_{in} + (\bar x\bar y +xy)C_{in}$ | |

| $=$ | $(x\oplus y)\bar C_{in} + \overline{(x\oplus y)}C_{in}$ | |

| $=$ | $(x\oplus y)\oplus C_{in}$ |

where we have used equation ($\ref{xorbar}$) above.

Next, form the SOP for $C$ to get:

| $C$ | $=$ | $xy\bar C_{in} + \bar xyC_{in} + x\bar y C_{in} +xyC_{in}$ |

| $=$ | $xy(\bar C_{in}+C_{in}) + (x\bar y+\bar xy)C_{in}$ | |

| $=$ | $xy + (x\oplus y)C_{in}$ |

The gate network is shown directly below.

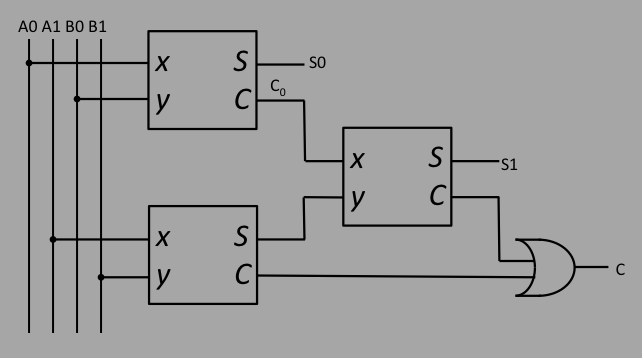

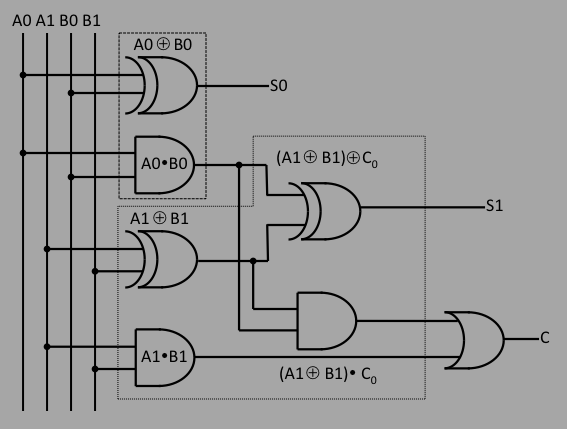

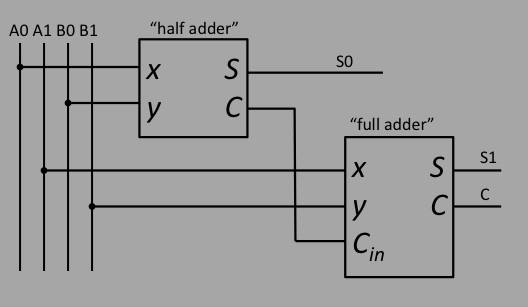

Note the dotted boxes in the figure above group $XOR$ and $AND$ gates that are equivalent to 1-bit adders. This shows the power of constructing "primitives" such as 1-bit adders to be hooked up to form 2-bit adders, as depicted in the figure below:

One thing to keep in mind here: because $C_0$ has to propagate through the 1st adder to get to the last one, we call this kind of circuit a "sequential adder". This means that when constructing such things, we have to keep in mind the time to propagate through real gates. While this can be fast (much less than a $ns$ in a modern FPGA), when constructing larger adders ($n-$bit adders where $n=16$ or even $32$) then there could be significan delays, and whether the delay is too large of course depends on the requirementes of the design.

Another way to group elements in the 2-bit adder schematic is shown in the next figure:

The smaller dotted box contains the regular 1-bit adder with 2 inputs, sometimes also called a "half adder":

and the larger box contains the 1-bit adder with the 3 inputs, aka "full adder":

We can put these 2 together to construct a 2-bit adder as shown below:

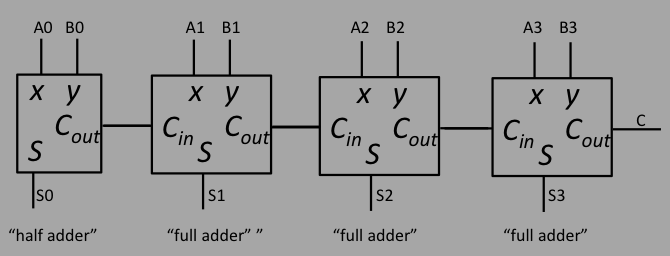

As you might expect, we can extend the pattern for the 2-bit adder to make an adder with any number of bits in analogy to how we can extend the algorithm for adding the 2-digit numbers together to any number of digits: add digits, save the carry bits, use it to add to the next highest bits until done. The following diagram illustrates how this is done for a 4-bit adder (adding 2 4-bit busses: $S[3:0]=A[3:0]+B[3:0]$. Note that we've redrawn the half and full adders to make the diagram more "linear", with the carry output of 1 adder flowing to the right into the $C_{in}$ input of the next one. This is sometimes called a "ripple adder", since the carry bit ripples through. As such, this is also a sequential adder that has a timing determined by the time through all the adders.

There are of course ways to build $n$-bit adders that are not sequential, and therefore faster. This will not be covered here, other than to say that in the world of digital logic and gates, there is a "phase space" that consists of number of gates $N$ vs total time through a circuit $T$, and that often it is the case that $NT=constant$. That is, one can make a circuit "faster" (smaller propagation time) but it will cost you gates. Or one can make a circuit "smaller" (fewer gates) but it will be more sequential and thust be "slower" (larger propagation time). Back to top

Useful Primitives | Back to top |

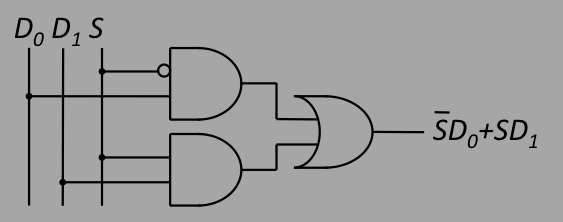

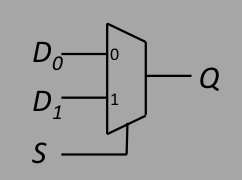

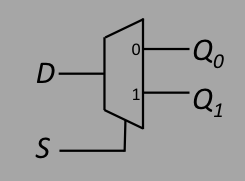

A "mux" is a circuit that takes 2 inputs, and depending on the state of a selector, connects one of the inputs to the output. A mux with 2 1-bit inputs, $D_0$ and $D_1$, will connect one of them to the output $Q$ depending on the state of the selector $S$. To be specific, when the selector $S=0$, then the output $Q$ is given by $Q=D_0$. When $S=1$, $Q=D_1$. This is called a "2-1 mux". The truth table would yield the equation $Q=\bar S D_0 + SD_1$ and the gate network looks like this:

The primitive looks like this for a 1-bit input and a 1-bit selector:

If we want to extend this to a mux with 2-bit inputs ($A[1:0]$ and $B[1:0]$), then since there are 2 inputs we still need a single selector (a selector that is 1 bit wide), so we would just use a pair of 2-1 muxes, one for $A0,B0$ and one for $A1,B1$.

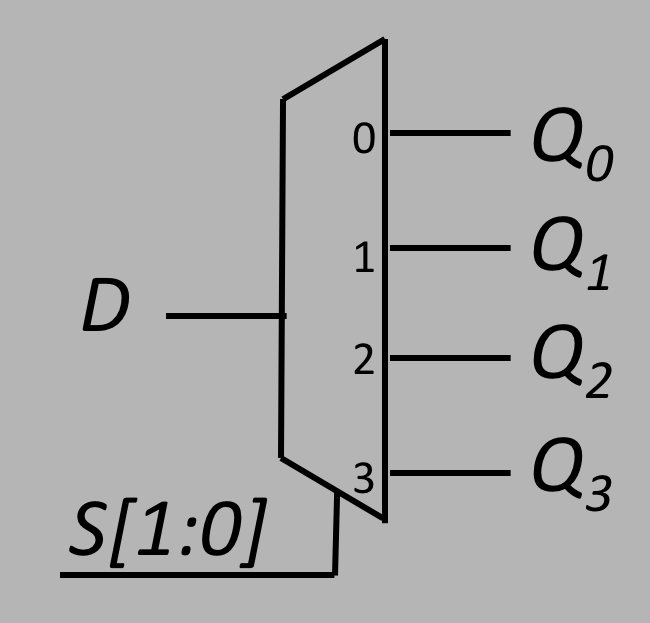

One can also imagine a mux that will connect one of 4 (or more) inputs to the output, The inputs will be $D_0$, $D_1$, $D_2$, and $D_3$, and the output will still be a single bit $Q$. Since we now have to choose between 4 inputs, we need a selector that is 2-bits wide: $S[1:0]$. This is a "4-1 mux", with the following truth table on the selector:

| $S_0$ | $S_1$ | $Q$ |

|---|---|---|

| 0 | 0 | $D_0$ |

| 0 | 1 | $D_1$ |

| 1 | 0 | $D_2$ |

| 1 | 1 | $D_3$ |

This gives us the following equation for the output: $Q=\bar{S_0}\bar{S_1}D_0 +\bar{S_0}S_1D_1 + S_0\bar{S_1}D_2 + S_0S_1D_3$ and the following for the 4-1 primitive:

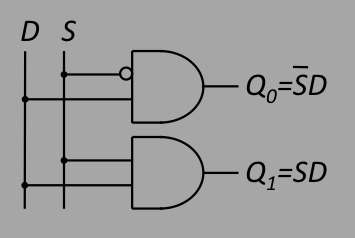

A "demux" is the opposite of the "mux": sending an input to an output depending on a select. The primitive looks like this:

What we want is a gate network that will send $D$ into $Q_0$ when $S=0$ and $Q_1$ when $S=1$, which means $Q_0=\bar{S}D$ and $Q_1=SD$. The corresponding network is:

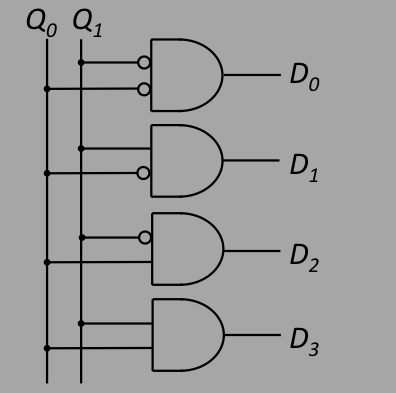

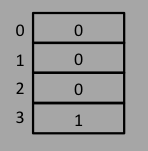

A decoder circuit will take a binary number and decode it to show which

bits are asserted. For instance, if you have a 2-bit number $Q[1:0]$,

the 4 possible numbers it could represent are $0,1,2,3$. A decoder will

have 4 outputs, say $D_0,D_1,D_2,D_3$, and will assert each of these

according to the value for $Q$. For example, if $Q=1$, then the decoder will assert

$D_1$ and deassert all the others.

The truth table, gate network, and primitive are below:

Interestingly, there's a correspondence between the 2-bit decoder and a 1-4 demux.

The latter looks like this:

A comparitor can be used to test the value of a number represented in gates. To make

things easy, let's construct a 1-bit comparitor using two signals, $A$ and $B$, and

forms 4 outline lines that are high ("asserted") when $A\!=\!B$,

$A\!\lt\!B$, $A\!\gt\!B$, and

$A\!\ne\!B$. The truth table for this is:

You should be able to recognize that the last column, $A\!\ne\!B$, is clearly an

exclusive or: $A\!\oplus\!B$. Similarly, the 1st

column, $A\!=\!B$, is clearly the inverse of $A\!\oplus\!B$. Using SOP it is

easy to see that the gates for

$A\!\lt\!B$ is $\bar A B$ and $A\!\gt\!B$ is $A\bar B$.

Back to top

Decoder

Truth Table Network Primitive

$Q_0$ $Q_1$ $D_0$ $D_1$

$D_2$ $D_3$

0 0 1 0 0

0

0 1 0 1 0

0

1 0 0 0 1

0

1 1 0 0 0

1

Comparitor

$A$ $B$ $A\!=\!B$ $A\!\lt\!B$

$A\!\gt\!B$ $A\ne B$

0 0 1 0

0 0

0 1 0 1 0

1

1 0 0 0 1

1

1 1 1 0 0

0

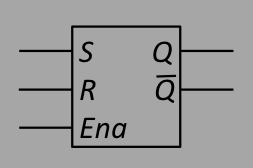

Memory (Registers) | Back to top |

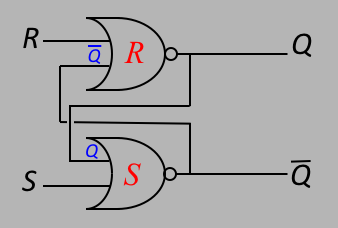

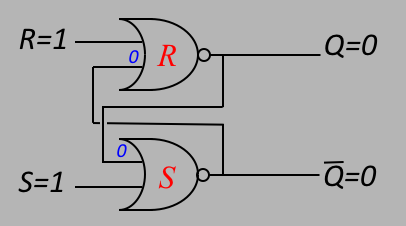

Imagine we construct the following gates to connect inputs $S$ and $R$ to outputs

$Q$ and $\bar Q$:

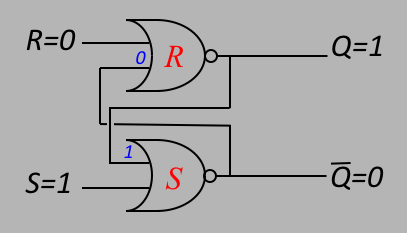

Now specify the input values: $R=0$ and $S=1$.

The inputs and outputs are shown below,

and the blue just follows the outputs.

You can see that since the bottom gate $S$ has

both inputs set ($S$ and $Q$

are both $1$), then if $S$ deasserts, $Q$ and $\bar Q$ remains the same, inverses of

each other. That's why we call this a "latch", because it latches the value

of $S$, and due to feedback, "remembers" it.

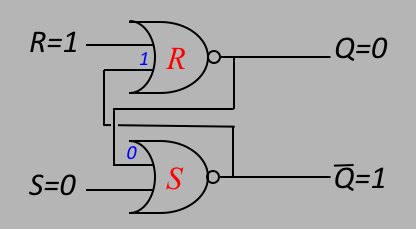

Now let's consider what happens when you are in the "set" state, $S\bar R$, and you

switch from $S=1$, $R=0$ to $S=0$, $R=1$. Let's analyze this by first asserting

$R=1$, seeing how the latch responds, then deassert $S=0$ and check again.

Setting $R=1$:

If instead of driving $R=1$ (and then $S=0$) you first drove $S=0$ (and then

drove $R=1$), giving $R=S=0$ as the intermediate state, nothing would

change due to the feedback.

The above combination is called a $SR$ "latch", or more precisely,

an $SR NOR$ latch. The "latch" means that the gadget "latches" the incoming

"set" and "reset" signals.

The function table, like a truth table, can be constructed like this:

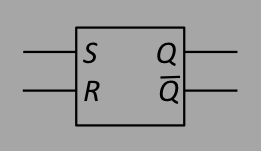

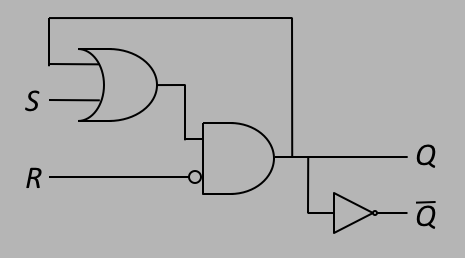

We can make an even simpler and more well behaved version of the RS latch

by constructing it from a single AND-OR gate combination, as in the figure

below:

When you set $S=1$, this turns on the OR gate (no matter what the other input

is doing), and if you set $R=0$, the AND gate turns on, setting

$Q=1$: the system is "set".

If you then turn $S$ off, nothing happens, the system "holds". If you

turn on $R$ ($R=1$), then that turns off the AND gate no matter what

$S$ is doing, driving $Q=0$. SO the truth table here is equivalent,

but simpler than the one above:

The "X" above means "don't care". $R$ is a true "reset", and once the

gate enteres the "set" state, it will stay there ("remembering") until

you drive $R=1$ to reset it.

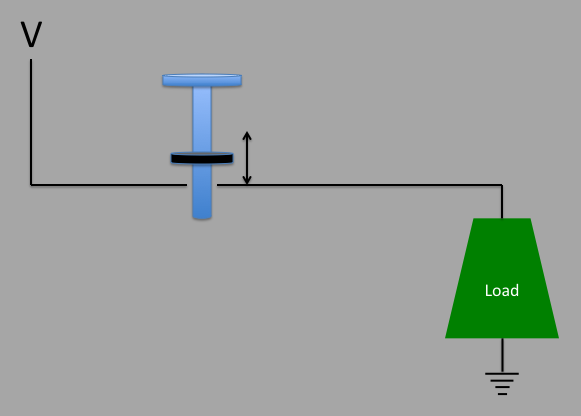

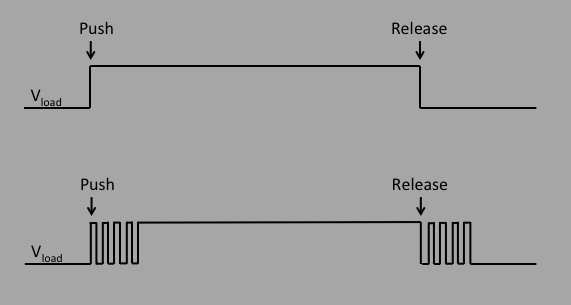

An example of where an RS latch can be very useful is as a "debouncer". So imagine

that you have a mechanical button, and when pushed it connects some output to a voltage

source as in the figure below.

Note that this debouncer is sending a digital signal to the load, so this

would technically be called a "digital debouncer". (That is, we are not

considering analog debouncers!)

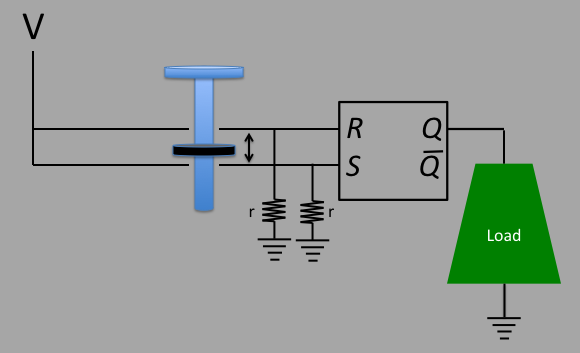

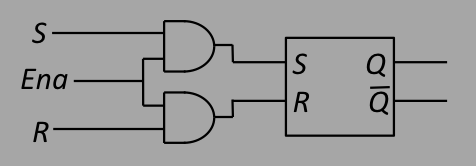

Sometimes you might want restrict the period time in which an RS latch is

active (that is, will respond to changes in $R$ and $S$). In other words,

you want to set up an "enable". This is accomplished by adding AND gates

to the inputs. The following shows the network needed to add the enable

ENA, and the resulting primitive:

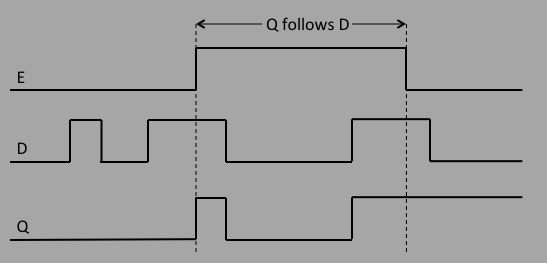

A "D-latch" ("D" for "data") is an RS latch where we take care of the $R$ and

$S$ being inverses of each other, and just use a data line $D$, with an enable.

The latch, when enabled, will have an output $Q$ that follows the data input

$D$:

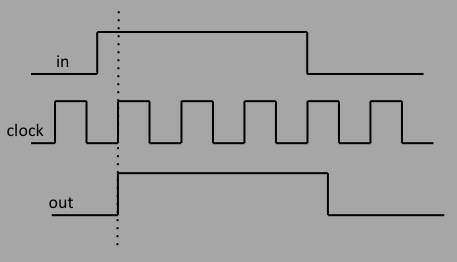

The waveform will look like this:

The output $Q$ will "follow" the input "D" only when $E$ (the enable) is

asserted.

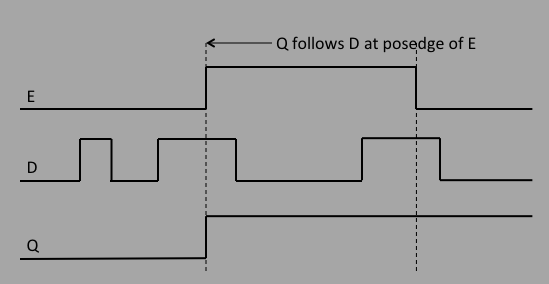

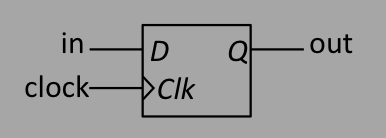

As seen above, the gated D-latch has an output that follows the input as long

as $E$ is asserted. But sometimes you just want to have the output follow

the input at a single specified time and not a range of times. For instance,

you might want to have a signal that transitions from 0 to 1, and at that time

of transition, you might want to have the latching happen. The diagram that

describes this is similar to the one above, except that the latch only happens

at the "positive edge" of the enable $E$, and anything later is ignored. This is

called an "edge triggered flip-flop", or DFF for short:

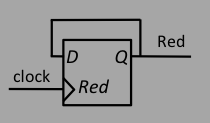

In the above primitive, instead of labeling the edge signal with "ENA", we label it

with "Clk", or "clock".

This brings up an important concept that is worth emphasizing: with edge triggered

DFF's, we now can implement what is called "synchronous logic", as opposed to the

previous implementions of what is called "combinatorial logic". In synchronous logic,

everything happens synchronously, or in sync with, some signal. And it is natural

to consider synchronicity in the context of some kind of "clock" that keep things

synchronous.

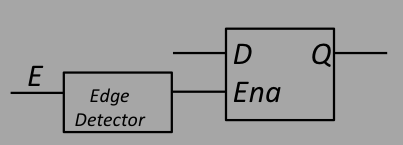

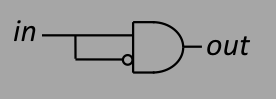

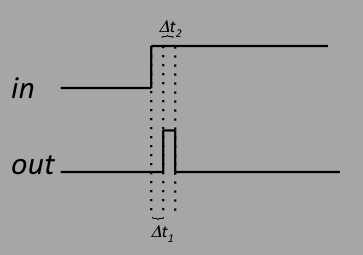

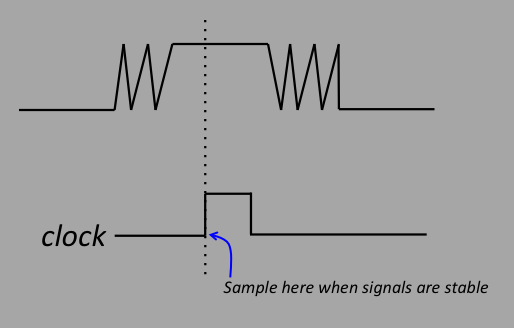

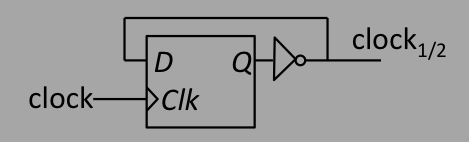

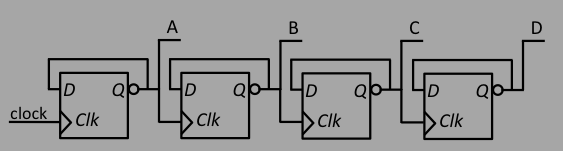

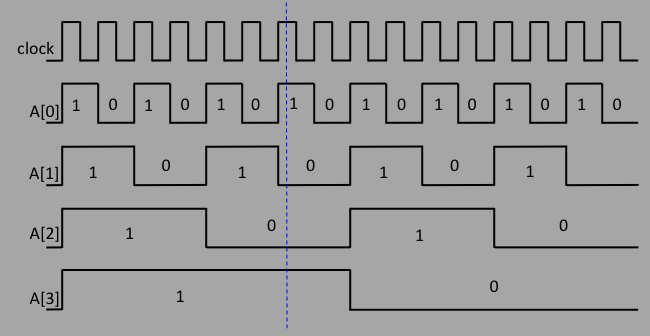

It turns out to be quite simple to make an edge detector. We start with the

circuit and waveform below:

RS (NOR) Latch

"Set" State

"Reset" State

This gives an output that has $Q=\bar Q=0$, breaking the symmetry that $Q$ and

$\bar Q$ are inverses of each other.

The figure below shows this intermediate state:

So the result, as shown in the figure below, has $Q=0$ and $\bar Q=1$, $Q=0$,

and again $Q$ and $\bar Q$ are inverses of each other. This is called the "reset"

state.

$S$ $R$ $Q$ $\bar Q$

function

1 0 1 0 set

0 1 0 1 reset

0 0 $Q$ $\bar Q$

hold

1 1 0 0

$Q\ne\bar Q$

RS (AND-OR) Latch

$S$ $R$ $Q$ $\bar Q$

function

1 0 1 0 set

X 1 0 1 reset

0 0 $Q$ $\bar Q$

hold

Debouncer

Gated RS Latch

Gated D Latch

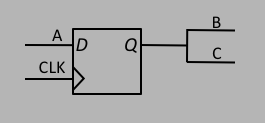

D Flip-Flop (DFF)

Figure 1, the D-flip flop.

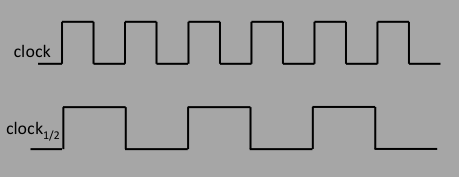

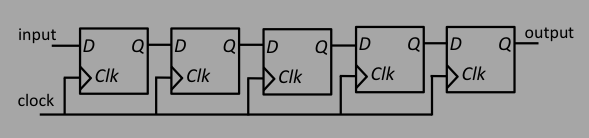

Synchronous Logic | Back to top |

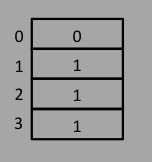

|

|

|

|

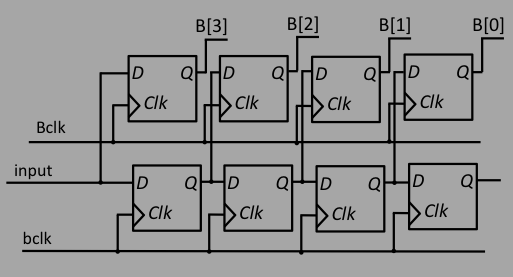

What could this be used for? One example is in serial to parallel data transmission. Imagine you are sending a serial 4-bit signal, and you want to decode it to know what the 4 bits are. These 4 bits will come in 1 by 1, at some rate synchronous with a "bit clock" ($bclk$). You place them into a 4 DFF long shift register, form a "byte clock" ($Bclk$) that is $1/4$ the "bit clock", hook it and latch the byte into a 4-bit wide "byte register as in the figure below. We are assuming that the bits arrive such that bit 0 comes first, followed by bit 1, 2, and 3, and repeats. The nomenclature is such that $B[3]$ is the 4th bit (MSB for "most significant bit"), and $B[0]$ is the 1st bit (LSB, for "least significant bit").

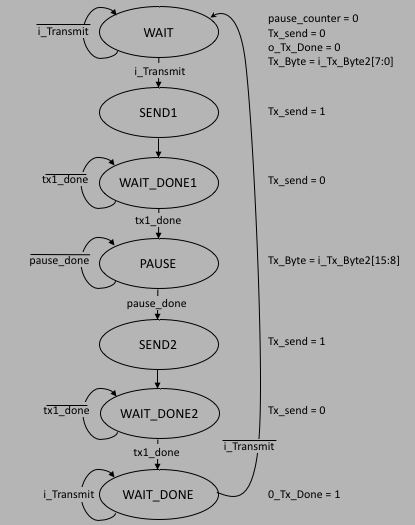

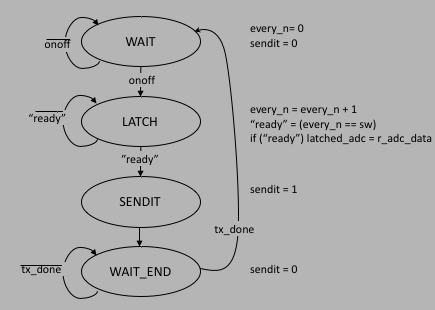

(Finite) State Machines (FSM) | Back to top |

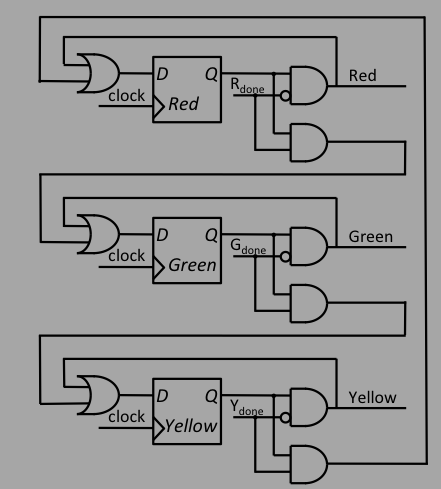

The classic example is a traffic light control. Here we have 3 states: red ($R$), green ($G$), and yellow ($Y$). The machine will step through these states in a definite order ($R\to G\to Y$), and will turn on and off the red, green, and yellow traffic lights.

It is often helpful to diagram the FSM to help visualize what happens when. Our traffic controller FSM would look like this. The "Red", "Green", and "Yellow" table enters are color coded to represent their values in each of the 3 different states.

Pretty simple and straight forward, but how do we construct such a thing? We start by using DFFs to store the state, and a build a logic network for the transitions and controls.

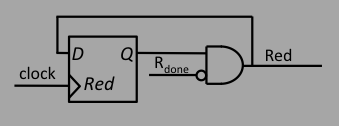

Let's start in the red state. We use a DFF with a preset of 1 (preset to be on) with feedback to "hold". The circuit looks like this:

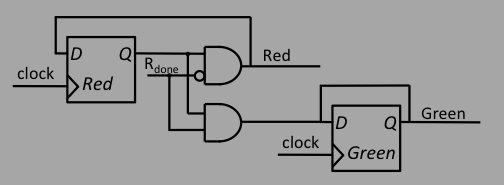

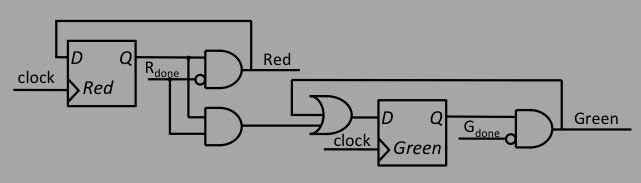

When the red timer Now we have to add the transition to the green state, which happens when the state is $R_{done}$ goes off, the state should transition, so it is no longer in the red state. That means you have to turn the red DFF off. The circuit to accomplish this would look like this:

Keep in mind that there will be propgation delays through the dates, so care should be taken to make sure that we don't inadvertently turn on two lights at the same time! And that one should try to have the clock inputs in such a way that the positive edges of each clock occur at the same time. This is easy to do, however, since the traffic FSM will not need $\mu$sec precision, so all you have to do is use a "fast" clock, which implies counters that are large to count macroscopic times.

A timing diagram is a very good complementary way to help describe how you want a state machine to behave. For our machine, we show the clock, the inputs from the red, green, and yellow timers ($R_{done}$, $G_{done}$, $Y_{done}$), and the outputs that turn on the lights, timers, and reset the timers ($Red$, $Green$, and $Yellow$).

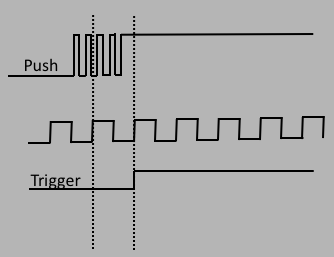

Note that the $R_{done}$ pulse is generated from the condition that the red counter is

finished (as a countdown counter, it's the condition that all bits are 0). But once

that condition is met, $R_{done}$ should stay high as long as the counter is at 0.

What is shown, however, is a pulse. This is a common thing to do to control things

carefully: we make $R_{done}$ a pulse so that we don't have any problems with illegal

states and illegal transitions. This "just in case" technique is a matter of taste,

however it is always wise to never leave active signals in the active state even

though you think nothing is paying attention to it! How we change $R_{done}$ from a

level to a pulse is easy: we implement something called a "one-shot".

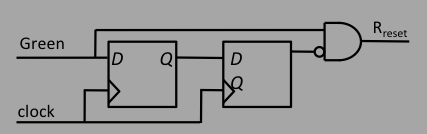

One Shot

The diagram below shows how to build a "one-shot", a circuit that changes a level into

a pulse. As pertains to the traffic system, when the green state is entered, GREEN

is asserted, and we want the red timer to be reset (reset to its preset value, and

ready and waiting to start counting). Before GREEN is asserted, the lower part of

the AND gate is asserted. Once GREEN goes high, then the gate turns out, and the

output $R_{reset}$ follows GREEN. Once the GREEN signal gets through the 2 DFFs, the

AND gate turns off and so does $R_{reset}$, turning the GREEN level into a $R_{reset}$

pulse. Once the red counter is reset, $R_{done}$ will also no longer be asserted,

and it will transition to 0 (as in the diagram).

Programmable Logic | Back to top |

Necessity is the mother of invention. Take a look at the following truth table that implements and AND gate:

| x | y | xy |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Modern FPGAs can contain the resources for making the equivalent of millions of gates, allowing all sorts of things to be implemented, even small 8-bit CPUs. They also have dedicated RAM to be used for memory purposes called "block ram", or BRAM, with upwards of many MBytes. They can have clock managers ("digital clock managers") that allow clock cleanup, phase adjustment, and clock multipliers, and some have built-in hardware arithmetic and modest CPUs. Back to top

Download Vivado | Back to top |

Befor getting into HDL, you should first download and install the Xilinx program Vivado. For this tutorial (2017), it is recommended you get Vivado 2017.2 (or .higher). To do this, either follow this perscription:

Run the appropriate installer, and set up a license. It is ok to get the 30 day trial license, but for the longer haul you should set up a better version, and as far as I know, at this time the licenses are free.

Hardware Description Languages (HDL) | Back to top |

The task of using FPGAs consists of 2 important steps: 1) deciding on the logic you need to implement, and 2) implementing it on the specific chip. Part 1 is your job, consisting of either drawing the gate network using some kind of palette and putting things together, or writing code in some higher level "hardware description language, or HDL". HDL, an a specific implementation called "Verilog", is what will be introduced and covered in this section. Part 2 is the job of the company that makes the FPGA, and will consist of several steps: 1) synthesis of the output of part 1, your part, to figure out the list of gates and DFFs etc that you will need, and how they are connected (a "netlist") so as to implement the logic that you want, and 2) a "place and route" (PAR) that determines how and where to place the resources needed and how to route the signals from one place to the other, relative to whatever specific FPGA you are going to use to implement the deesign. This PAR step can take a lot of CPU time depending on the nature of the job, how "full" the FPGA is (fraction of resources used) and what the constraints are for meeting timing goals.

There are 2 basic HDL languages that are used, called VHDL and Verilog, and they are both born from the need to simulate designs. Verilog was developed by players in the private sector in the early 1980s for simulation, and the name comes from the synthesis of "verification" and "logic". The language itself began as a proprietary product owned by Cadence, and was put in the public domain as an IEEE standard in the mid 1990s. VHDL on the other hand was developed by the DOD for ASIC (application specific integrated circuits) production, all the way down from the logic to the hardware level. In VHDL you can specify things like transition emitter rise time, and other things that have nothing to do with the design logic. As such, VHDL has many more constructs (syntax) than does Verilog, which makes it both richer and more complex. For pure programmable logic, implemented on FPGAs, many find Verilog to be easier to use, but this is just an opinion (that of course borders on religion for some of the more focused people!). We will focus on Verilog here.

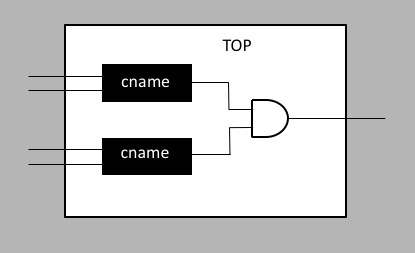

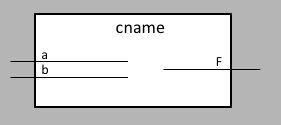

But basically, you should think of the code in terms of circuits: the code defines circuits,

which means inputs, outputs, and what's in between. The following picture shows a top level

circuit called "TOP", with 2 inner circuits named "cname". TOP has 4 inputs (on the left) and

1 output (on the right), cname has 2 inputs in the left and 1 on the right. None of the inputs

are labeled now. The syntax is:

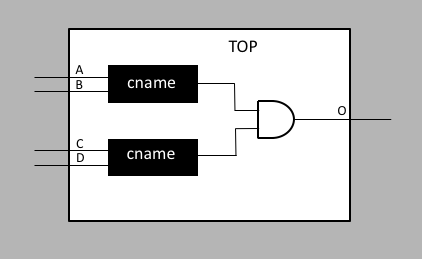

First lets define the inputs as A, B, C, D, and the output as O, and use the usual

Verilog syntax for defining the top level "module" which we will call "TOP".

The

syntax structure is the following:

We don't yet know what "wire" means, but that will come next.

There is no semicolon after the "endmodule", but there is after the "module" at the beginning.

"name" can be anything, and the inputs and outputs are specified inside the parentheses.

Below the "module" declaration, you specifiy which are inputs and which are outputs, and then

whether they are wires or regs (see below). Note that the above syntax is pretty much from

the original incarnation of Verilog, which is evolving, so of course there's a more compact

way of doing the above:

Now that you have the TOP circuit coded up, you have to also code up "cname".

We don't know what's inside of "cname", and we don't need to know that yet, but we do have to

know that it has inputs and outputs. So we label the inputs as "a", "b", and the output

as "F". The following figure shows the cname circuit:

Verilog has a nice way to get around this potential disaster of wiring the inputs

wrong from the top level module where the circuit is instantiated. For instance, you might

have wanted to instantiate it as "cname CNAME1(B,A,c1);" instead! So to get around

this potential for disaster, Verilog have an alternate way of wiring up inputs and outputs

from one circuit into another. The new way is shows below:

We specify the lines as "wires", and these are objects that can be thought of as being just like real

wires in circuits - the wire will be driven by something (like an AND gate) and will have a value

(or state) of 0 or 1. Note that wires only carry the value from the thing that drives them.

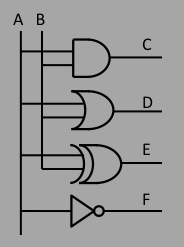

From the above figure with inputs A,B and outputs C,D,E,F, the first piece of Verilog syntax will be:

Now comes the part that contains the logic you want to implement.

In Verilog, we have the following representations of operations and

operators:

That's it! Pretty simple.

As an aside...why does Verilog have an "assign" statement and not require it? It's because

of the history of Verilog, and it's original usage, which was as a simulation language.

Imagine writing some computer code to simulate a digital network (like the one we just

invented above, with TOP and cname). You would have to have some kind of timescale "tick",

and at every tick you see what the signals are doing, and propogate things to the next time.

If your simulation consists of 4 inputs, 1 output, and a couple of internal wires, then it's

easy. But if the simulation is more complicated, then to check everything at every time tick

will be exceedingly slow.

So Verilog, originally a simulation language, solves this by inventing the "assign" statment.

Here's how it works for the statement

Now let's make a new design that uses everything we've learned, and write code that

instantiates the following circuit:

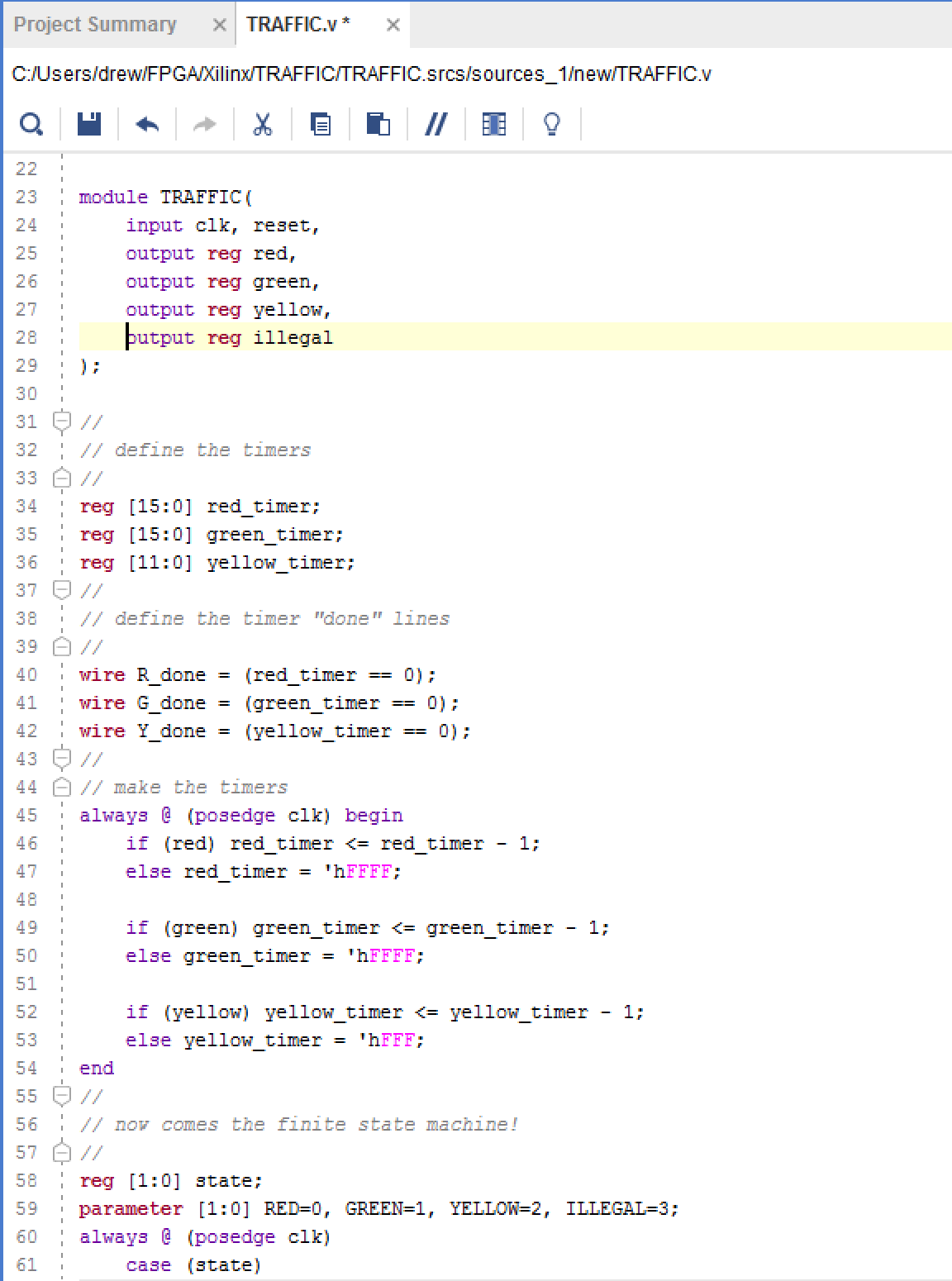

We are ready now to code up the finite state machine (FSM) that we invented for the traffic light.

For this project, we will need an externally provided clock input, and let's put the frequency

(arbitrary, but we have to pick something) at 1kHz, or 1.0ms time period.

Now, let's set the time for the lights to be (roughly, this doesn't have to be exact)

30s for green, 30s for red, and 2s for yellow. That means we need to wait $30s/0.001s=30,000$ ticks

for the green and red light, and $2/0.001=2,000$ ticks for the yellow.

This dictates that we need a 15 bit counter: $2^{15}=32768$, which means it will count for

$32.768$ seconds, which is close enough. For the yellow light we need an 11-bit counter:

$2^{11}=2048$ which means the yellow light will be on for 2.048 seconds, also close enough.

Let's make a top level module called "TRAFFIC", and have 1 clock input and 3 enables for the

3 different lights:

The timers are instantiated like this:

Now that we have the timers and the timer done lines, we can write the code that

controls those timers. Since the timers are registers, we implement it in an always

block. We need an enable line that controls when to allow the timer to count down,

and what to do when the timer is not counting (reset to all 1's). The code

for the red timer will look something like this:

Also, note that in the ILLEGAL state, we specify all of the outputs,

not just the red light. This is because if we got into ILLEGAL, we don't

really know how that could have happened (an electrical glitch?), so we

want to be sure we are controlling everything.

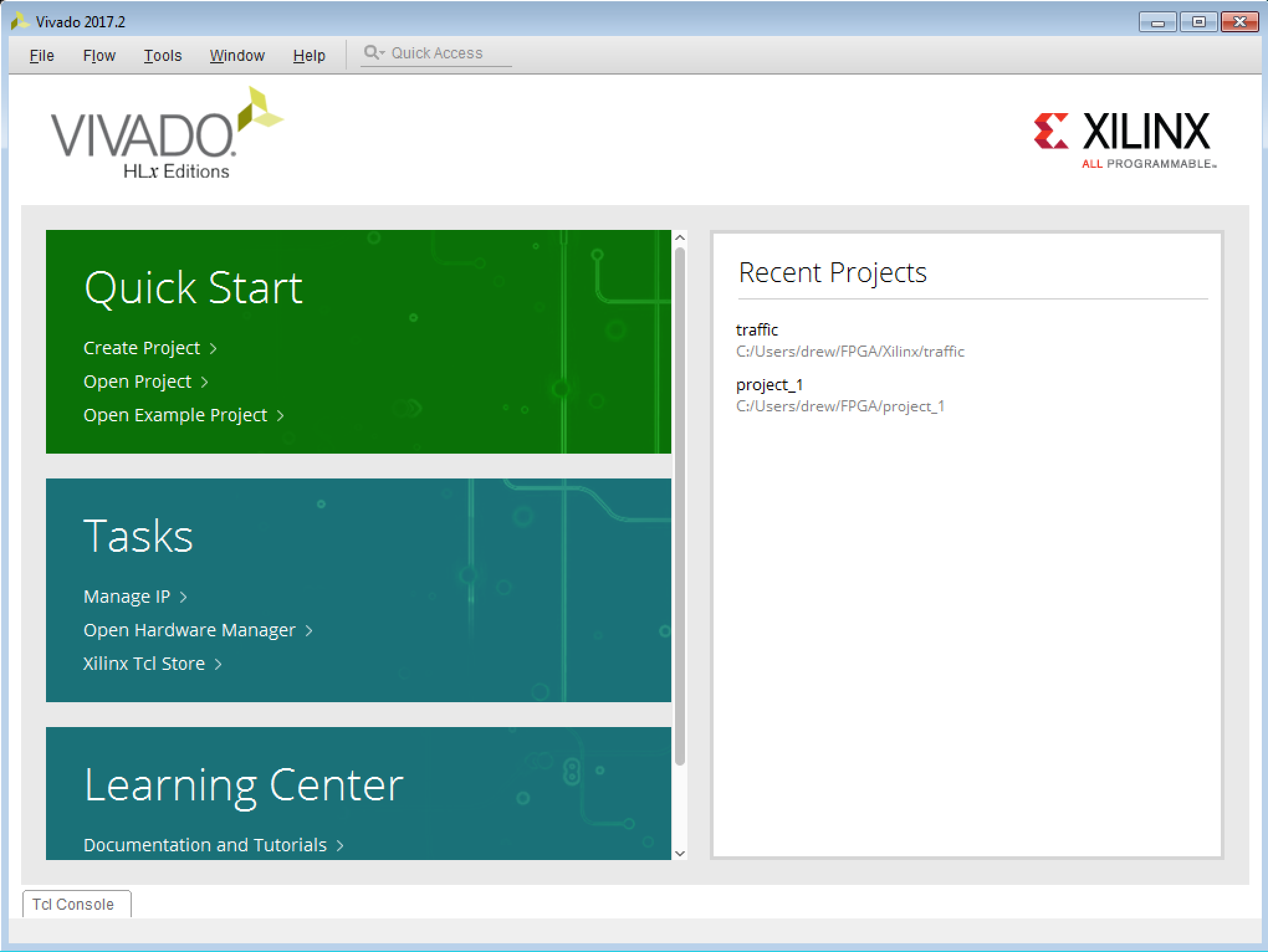

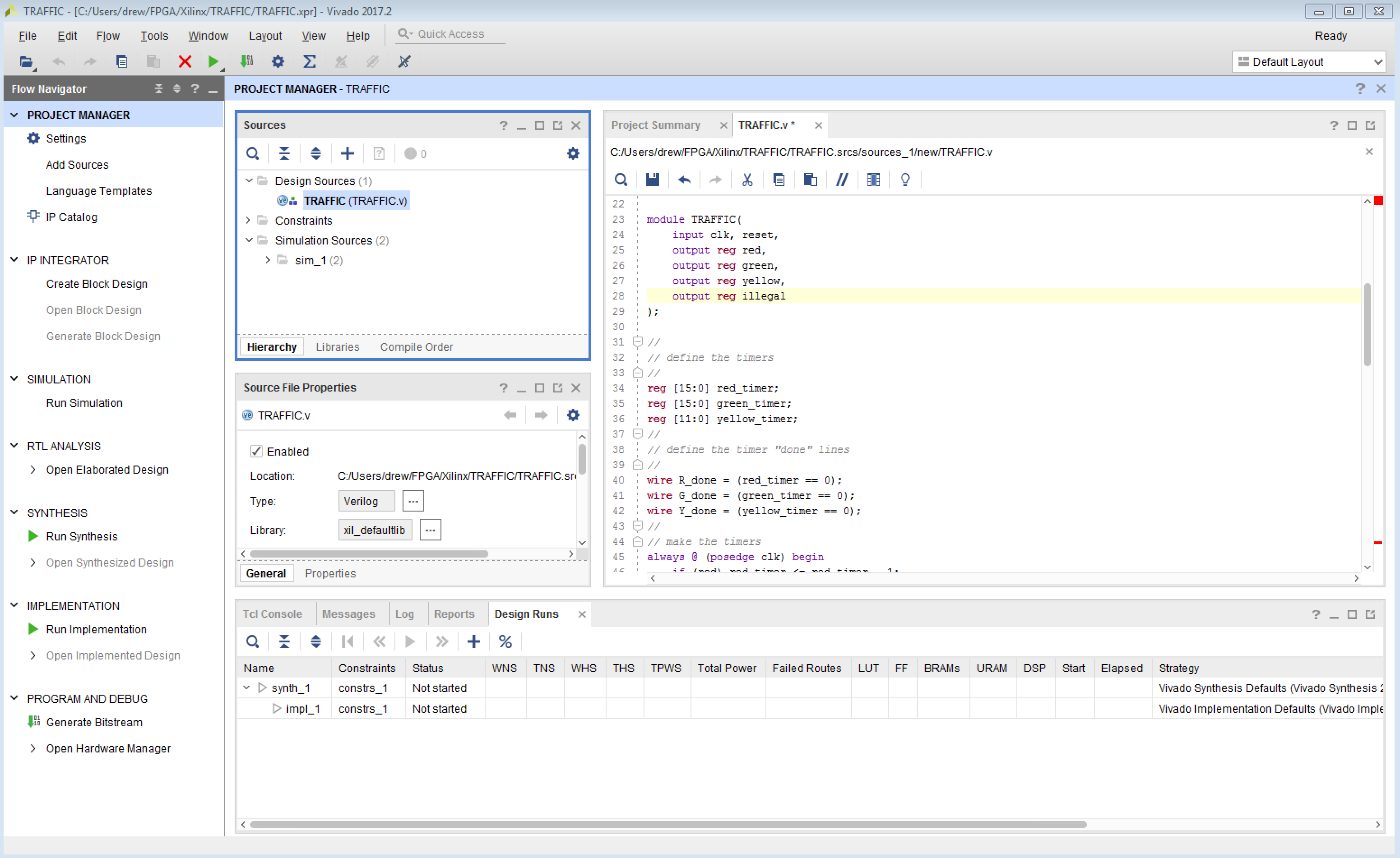

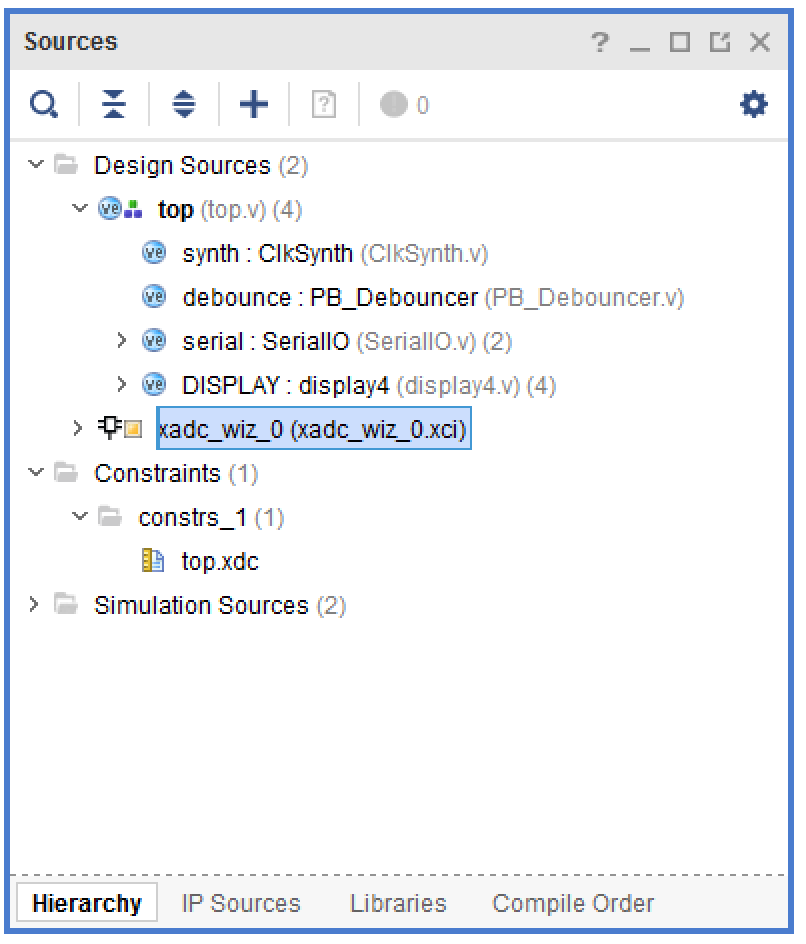

We now have to start using the Xilinx Vivado program. The version

here (2017) is v2017.2 running on a Windows machine. See

above for instructions on how to download and install. Once that is complete, and you have

a valid license installed, run Vivado "HLx" (not "HLs"!).

When you run Vivado, you should see the following screen:

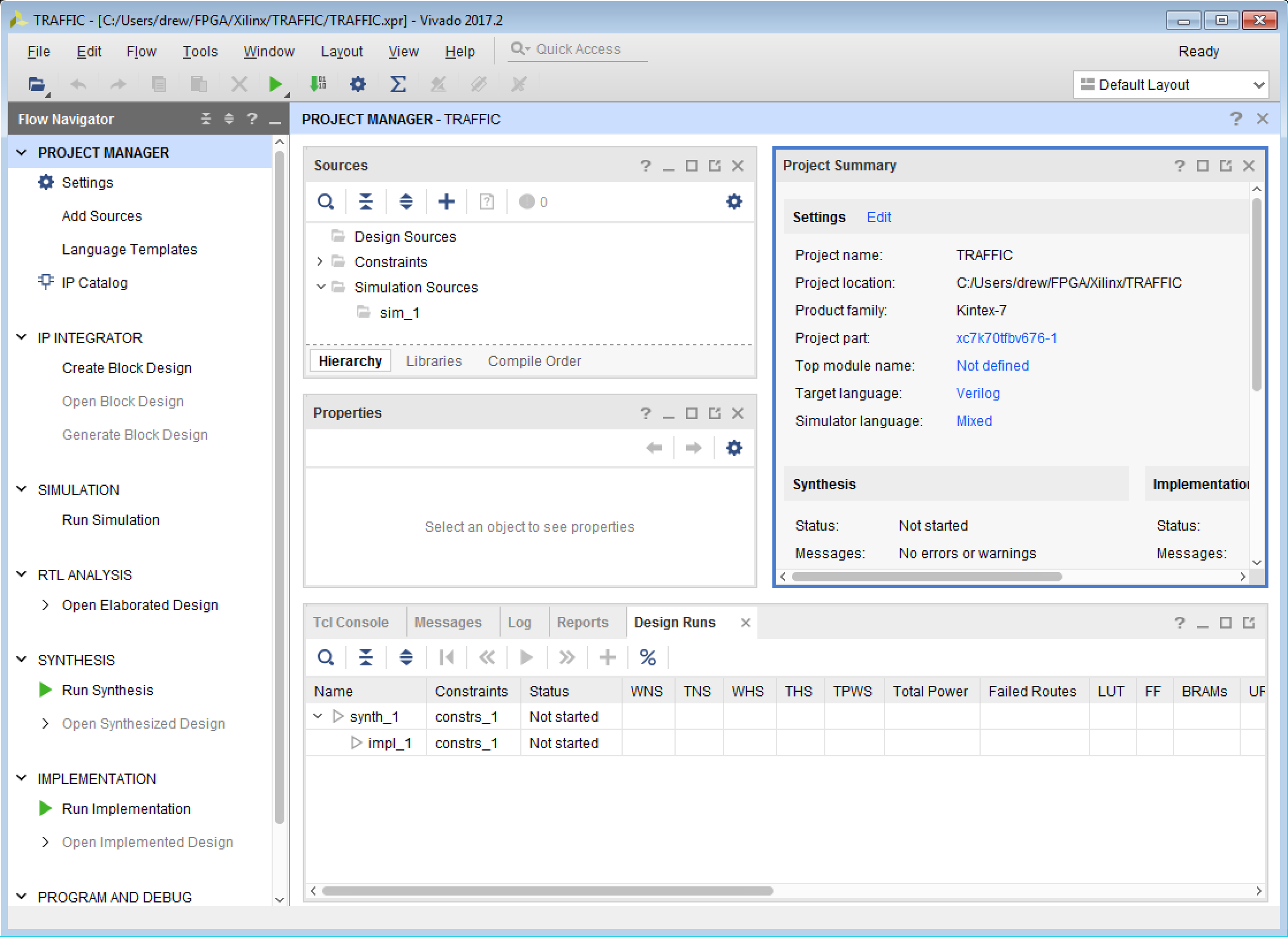

The next screen is called "Project Type". Click on the 1st radio

button labeled "RTL Project", and hit "Next".

Next you will go to "Default Part". This is for people who know

the part name of the FPGA they will be programming. In this case,

we don't really care about the actual FPGA, so just it "Next"

without specifying anything. That takes you to the final window

where you can hit "Finish". You should now be at a window that looks

like this:

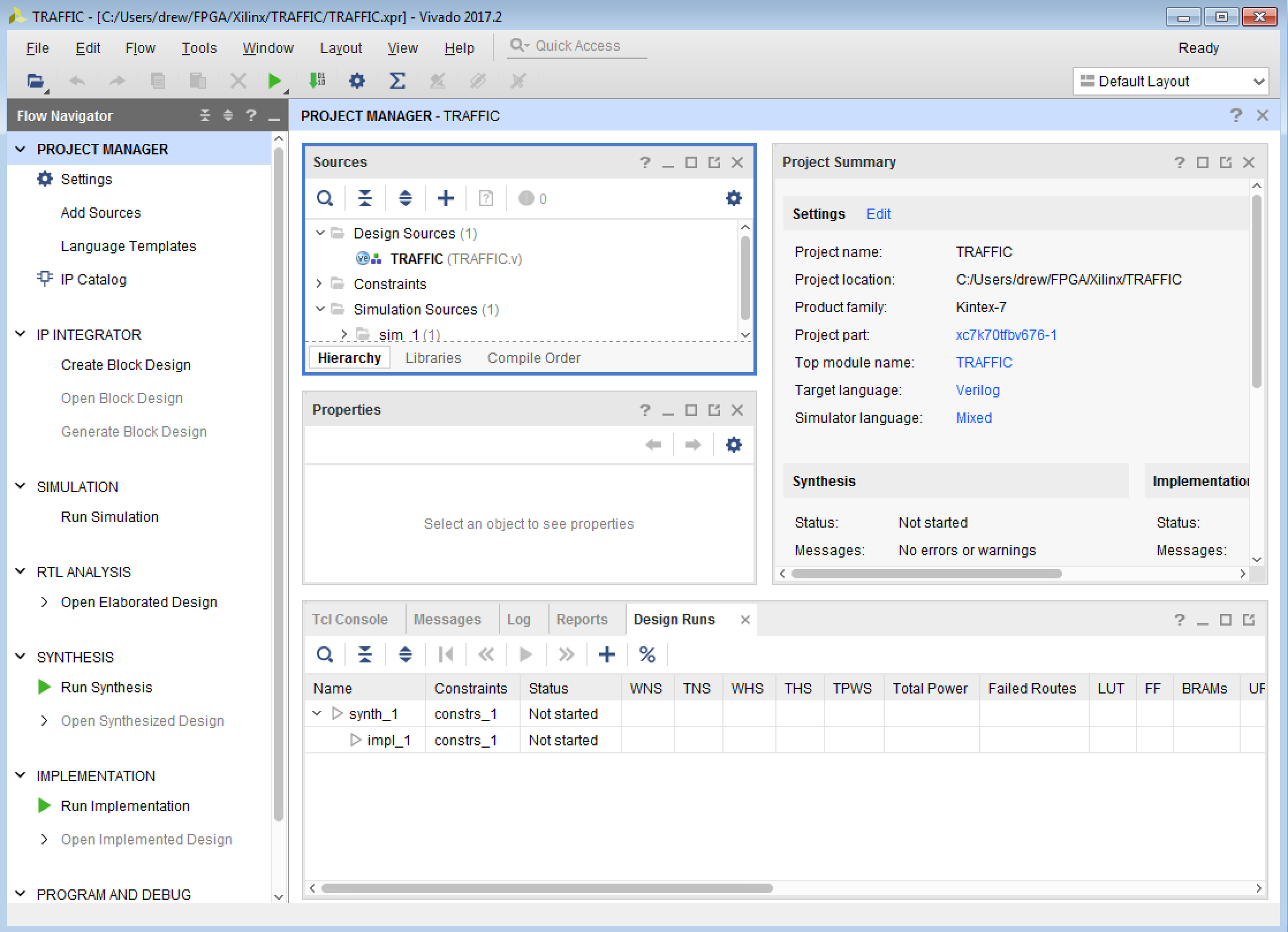

Now we need to add some source code. If you mouse over

the "+" sign in the "Sources" subwindow, it should say "Add Sources (Alt+S)".

Click there to bring up the "Add Sources" window. Make sure that

"Add or create design sources" is set, and hit "Next". This brings up a

window called "Add or Create Design Sources". Since you don't have any

sources, you want to click on the box called "Create File", as seen

below:

The Vivado window should now look like this:

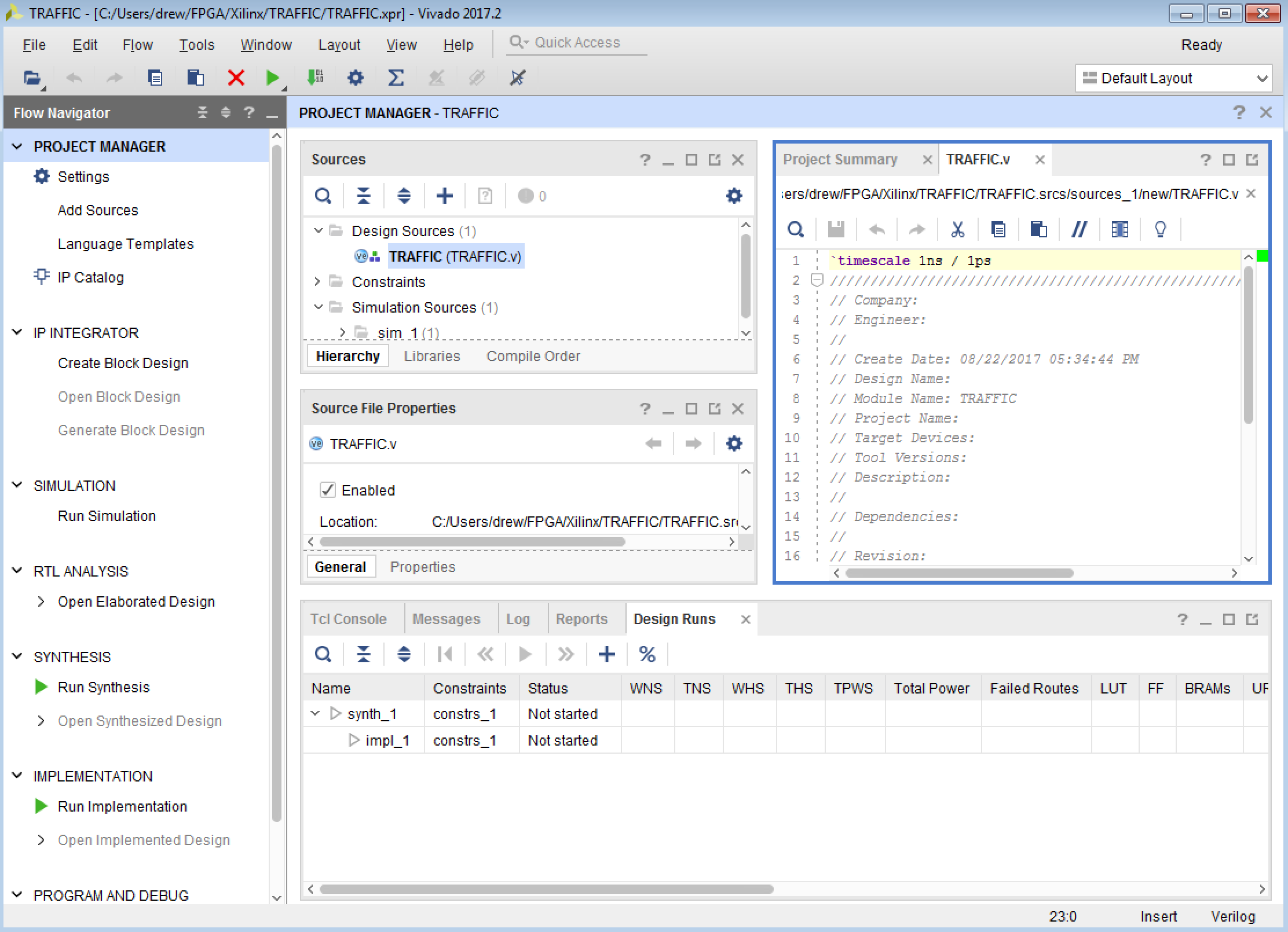

The top line of TRAFFIC.v has the following line of code:

Now go to the traffic FSM you coded up earlier, paste that into

the edit window, and save it (control-S).

It should then look like this:

Before you take any Verilog code you've written and run it in an FPGA, you

should always run a simulation and look at waveforms. This is really

important for any successful programmable logic project, because as we know

form Murphy's law, nothing ever works correctly the first time.

Let's use the FSM for the traffic lights that we wrote in the previous

chapter. We will simulate it using the standard tool that comes in the

development tool from Xilinx (or Altera, take your pick), but first we

have to write our own "stimulus". That means we need to write some

Verilog that controls the inputs to our circuit ("TRAFFIC"), and checks on

the outputs, and presents them in a viewable waveform. There are tools

that allow you to generate stimulus using waveforms directly (pointing and

clicking), however it's much more powerful to use Verilog directly, and

the bottom line is that a simulation is only as good as the ability to

faithfully represent the inputs.

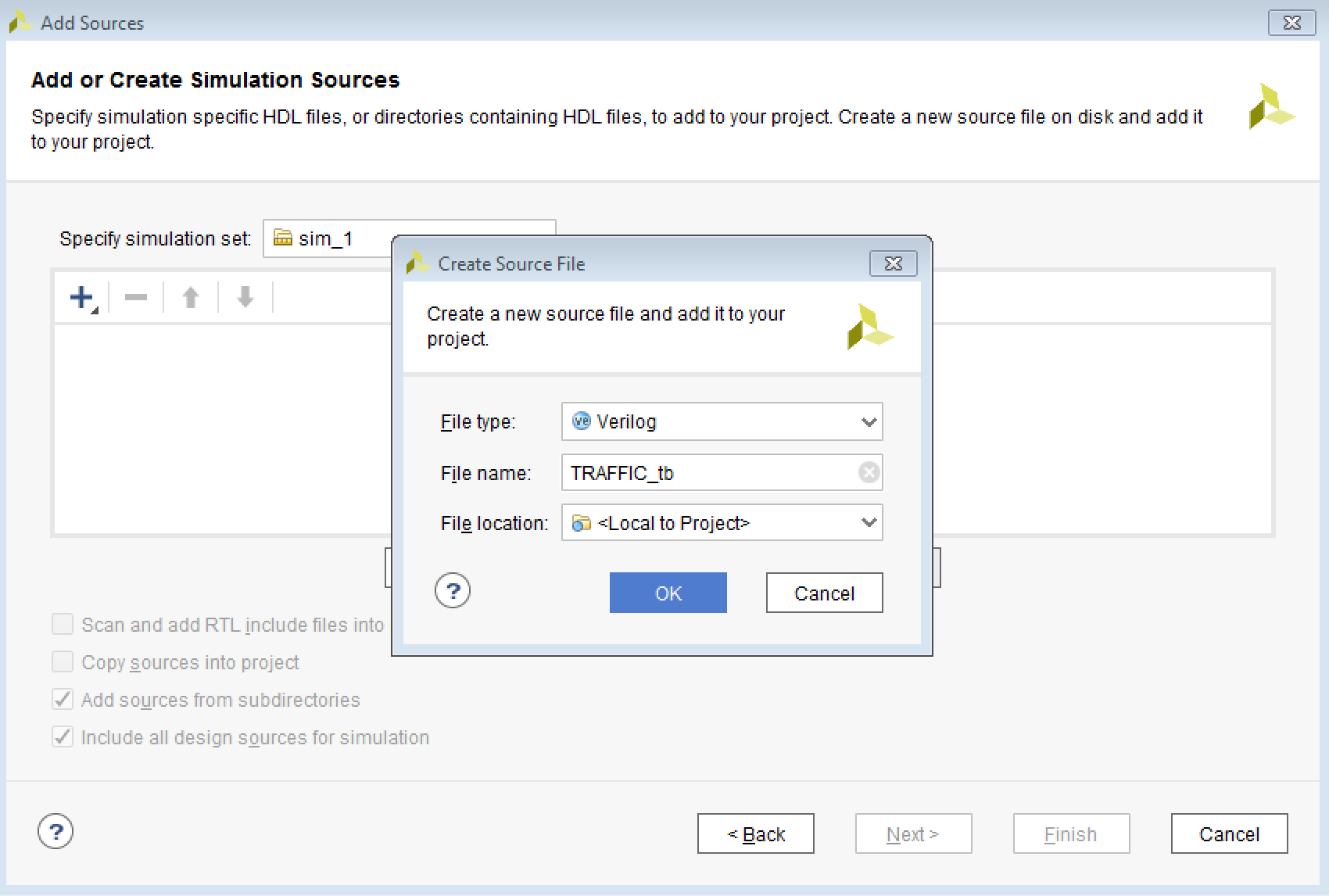

To generate the testbench, we first generate a new source file that

will be plugged into the project. In the same "Sources" subwindow

that you used create the TRAFFIC.v source, click again on the "+"

button to bring up the "Add Sources" window. This time click on the

3rd choice, "Add or create simulation sources",

and click "Next". The brings up the "Add or Create Simultion Sources"

window, where you click "Create File", which brings up a "Create Source File"

window where you can name the new source. Let's call it "TRAFFIC_tb"

("tb" for "testbench") and it OK. It should look like this before you

hit OK:

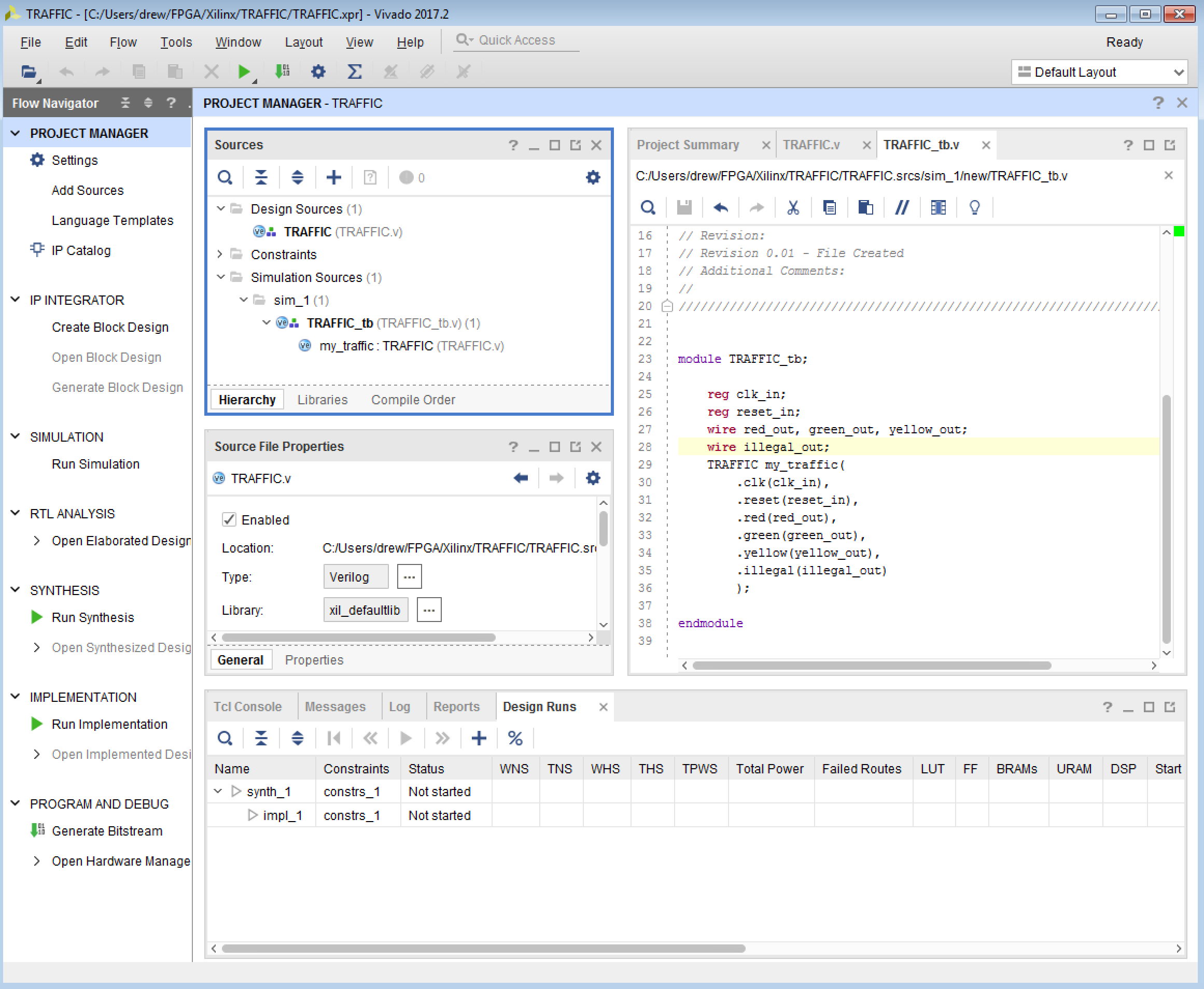

Hit OK and "Finish", and "OK" at the next "Define Module" window, and

confirm "Yes". Vivado should look like this now:

Next we have to edit TRAFFIC_tb.v to add the stimulus. To do this,

click on the ">" symbol on the line "sim_1". It should then show

you 2 files: TRAFFIC.v under "Design Sources"

and TRAFFIC_tb.v under "Simulation Sources". The latter is what will

use to stimulate the former.

If all is well you should see the correct hierarchy like in

the following, with "TRAFFIC.v" underneath "TRAFFIC_tb.v".

Double click on TRAFFIC_tb.v and it will create

a new tab in the subwindow to the right. That window should be

empty except for the timescale directive, some comments, and

the module declaration. Now we learn how to write Verilog stimulus code.

The first thing we want to do is to instantiate the TRAFFIC.v circuit,

and define the inputs that go

into TRAFFIC.v, so that we can stimulate them, and the outputs,

so we can see how they behave. We do this with the following code:

Next we want to specify the reset line, which is done in the following

code:

Now we are ready to run the simulation. In the left pane of the Vivado

window, you should see "Run Simulation". Click on it and you should see

a pop-up window. Click on the top line, "Run Behavioral Simulation".

What that means is the following: the verilog code for

TRAFFIC.v has no timing information (it's actually possible to add it,

but that's another story). So when AND and OR gates change state, and

DFFs see posedges, they happen "instantly". As such, the waveforms will show

the behavior of the logic, but won't tell you anything about actual timing.

Doing that is possible, but only after you've actually run the full

synthesis and implementation. I have found that most of the bugs are

found right away by doing a behavioral simulation. If you have timing

problems (so-called race conditions) then you probably won't see them in

any kind of simulation easily, you just have to run the thing in an FPGA

and do a first order checking there for mistakes before a real timing

simulation. Also, the timing simulation uses best guesses for the actual

delays inside the FPGA. And each FPGA is slightly different. Best to

find errors in situ first!

If you have any errors, the system will report it. On the bottom, you

will see a panel with 5 tabs labelled "Tcl Console", "Messages", "Log",

"Reports", and "Design Runs". You will have to wade through these to

figure out what the errors are, but usually it's just syntax. The

"Tcl Console" should tell you the exact errors.

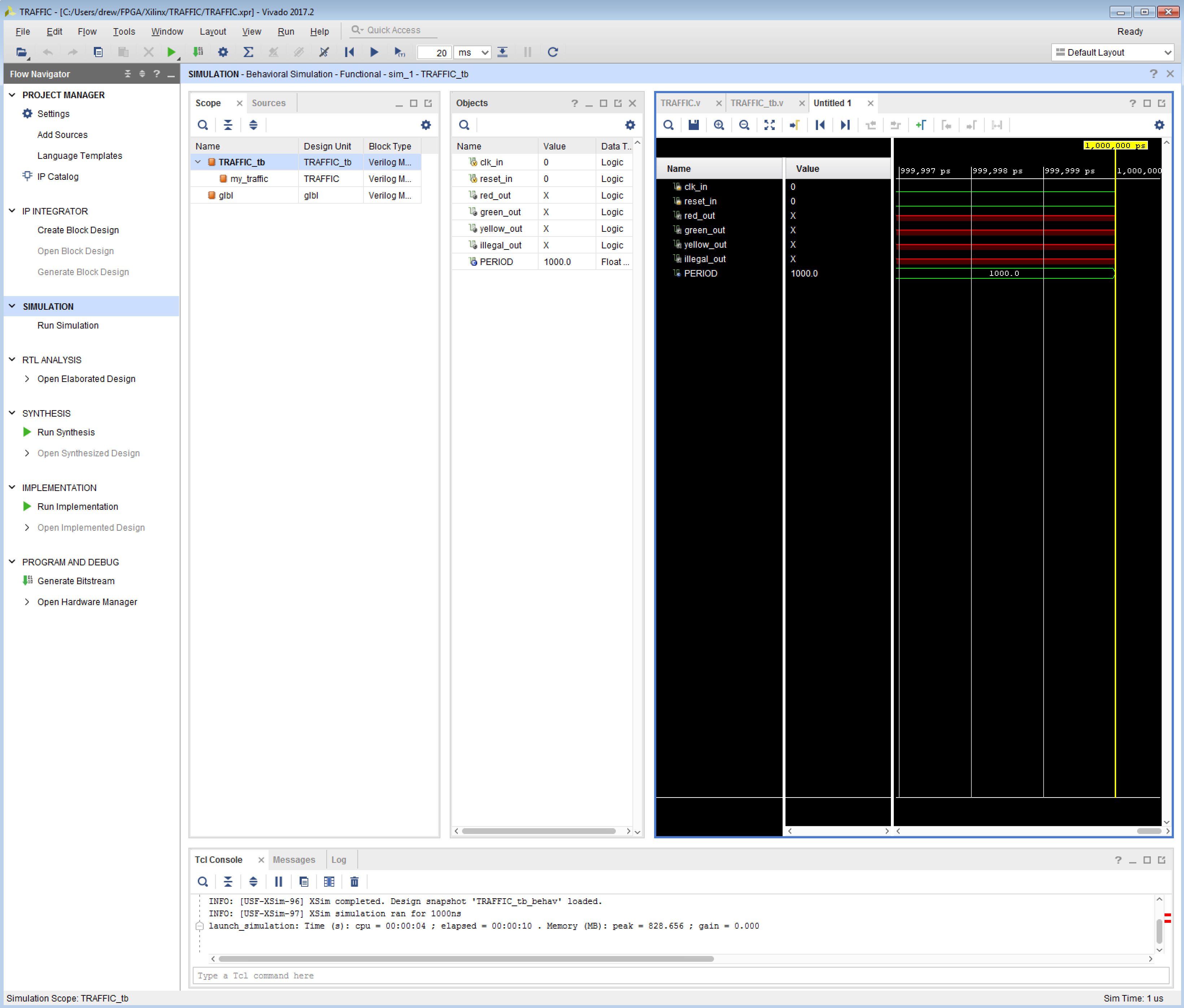

Assuming all goes well, you should now be looking at the following

rather large window:

The default scope is "TRAFFIC_tb", so you can see in the waveform window

all of the signals present in that source. You won't see anything

interesting yet, because the simulation defaults are not set correctly.

Notice on the top line of the window the usual tabs "File", "Edit", etc.

Towards the end, you will "Quick Access". There are 3 icons, then

a text window that says "20", then one that says "ms", then some other

icons. The first of the 3 is the "Restart" icon, for restarting the

simulation. The next one, a triangle, is "Run All" (run), and the 3rd

is a triangle with a little "m" below it, which means run for a time

period as specified in the next 2 windows, which means 20ms. Let's

change the "ms" to "s", click restart, and click run for 20s.

Now, go into the waveform window and click on the icon that is called

"Go to time 0" (when mousing over), and then keep zooming in (3rd icon,

circle with a + sign) until you can see the clock transitions, so the

vertical lines should be every 10ms or more. You should see something

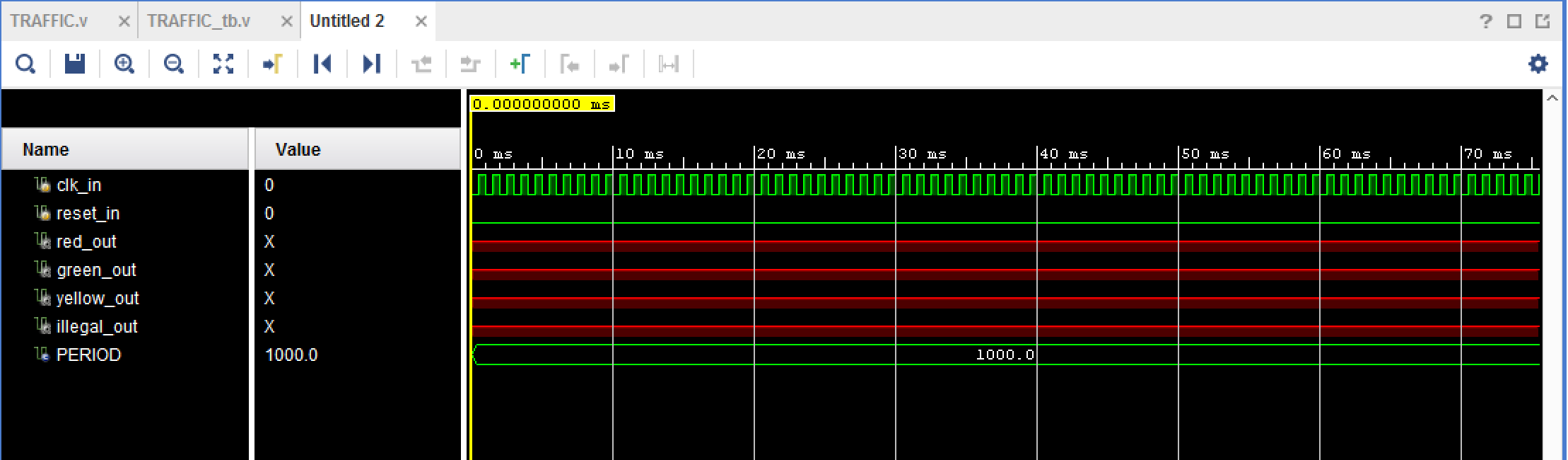

like this in that window:

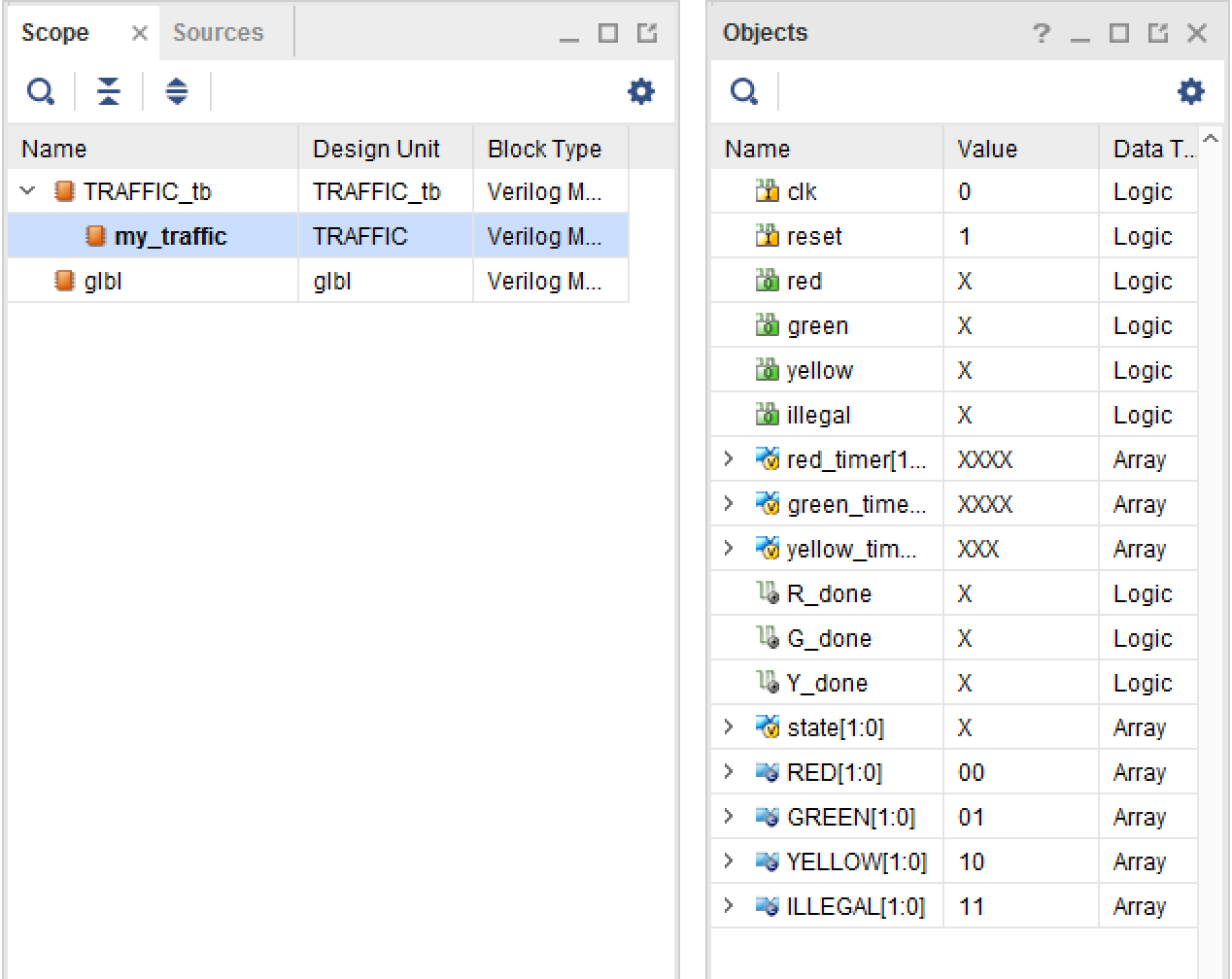

One nice technique to figure out what needs to be defined is to click

on the "my_traffic" scope in the Scope window. That will bring up all

the objects. You will see which have the value "X", as in the following

window:

Here, we want to do an asynchronous reset, because it's only going to happen

once. The first thing to change is the stimulus code:

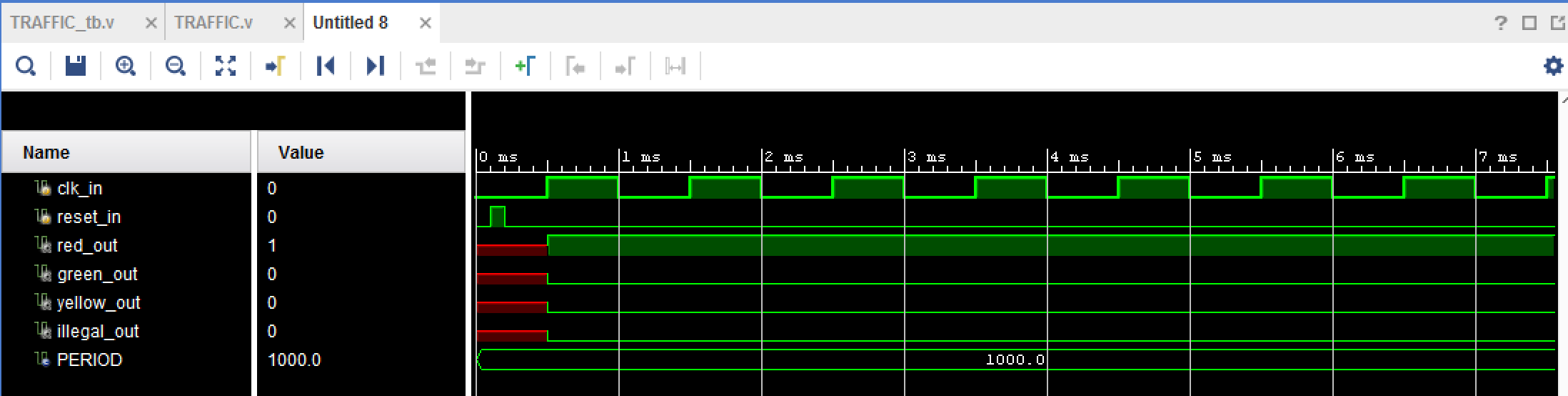

Now let's run the simulation for 200 seconds (change 20 to 200 in the

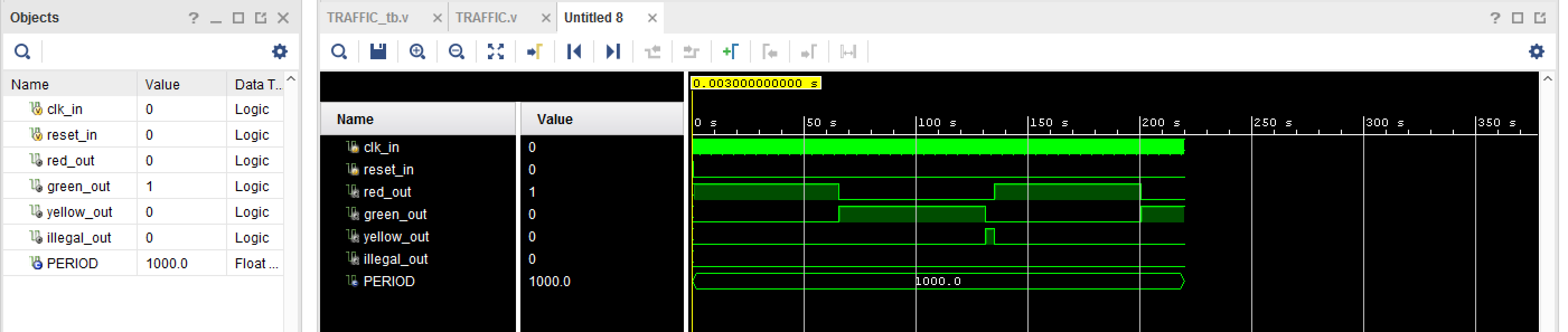

quick access part and rerun). Then zoom out a bit so you can see 200

seconds worth of waveforms. You should see the following:

You should also take a look at some of the objects in the TRAFFIC.v

source by clicking on "my_traffic" in the "Scope" window and dragging

those signals into the waveform window, and rerunning via the icons.

You can see something like the following, showing how the internal

signals behave. Below you see the state going through its cycle,

the timers running and reset to all 1s, the done lines, and so on.

Verilog Intro

When you learn Verilog, it is helpful to keep in mind that the syntax was invented for simulation

purposes, not for describing programmable logic designs. This will come in handy when learning

about how to code for flip-flops.

module TOP(A, B, C, D, O);

input A,B,C,D;

output O;

.

wire A,B,C,D;

wire O;

.

.

.

endmodule

and this maps to the following figure:

module name (

input A, B, C, D,

output O

);

.

.

.

endmodule

Note that there is no semicolon after "D", just a comma, since it's still within a declarative

list, and no comma after "O", since that is the last element in the list.

module cname (

input a, b,

ouput F

);

.

.

.

endmodule

We don't need to know what "cname" does yet, but we do need to know how to

instantiate it inside another circuit (called TOP). Do do that, the syntax is the following:

module TOP (

input A, B, C, D,

output O

);

//

// these are comments just like in c or c++!!!!

//

wire c1, c2;

cname CNAME1(A,B,c1);

cname CNAME2(C,D,c2);

.

.

.

endmodule

Note the syntax "cname CNAME1(A,B,c1);". This has the required semicolon at the end. The

first term, "cname", is the name of the module ("module cname(...)" as above). The 2nd

term, here "CNAME1" and "CNAME2" is the instantiation name. This can be anything, it's just

a way of differentiating one instance of a circuit from another. The arguments "A, B, c1"

and "C, D, c2" are names of the cname input/outputs as known inside TOP! This is an

important concept for how to specify the connections: if you use this syntax, then you have

to be careful that the order corresponds to the order inside the module.

.

.

cname CNAME1(.a(A), .b(B), .F(c1));

.

The ".a" specifies the name of the io port inside the instantiated ciruit, and the "(A)"

specifies what is wired to it. This is nice - it means you can't go wrong! So the overall

Verilog code thus far is:

module TOP (

input A, B, C, D,

output reg O);

//

// these are comments just like in c or c++!!!!

//

wire c1, c2;

cname CNAME1(.a(A), .b(B), .F(c1));

cname CNAME2(.a(C), .b(D), .F(c2));

.

.

.

endmodule

Wires

Next we have to discuss the Verilog syntax for naming gates. However, this is not

how it works! In Verilog (as is also the case in VHDL, the main competitor), you don't

name the gates, but instead you name the inputs and outputs, and use operators (&,|,^)

for the gates.

To begin, let's take the simple constructs of AND, OR, XOR, and NOT:

wire A;

wire B;

wire C,D,E,F;

Note the important semicolon at the end of each Verilog statement, required just like in C or

C++. (And like C or C++, if you forget the semicolon, you will get an error message in the

compilation that will not say "you left the semicolon off".)

Also note you can have 1 line per wire, or declare multiple instances of wires on the same

line.

Operation Operator

AND &

OR |

XOR ^

NOT ~

wire A;

wire B;

wire C,D,E,F;

assign C = A&B;

assign D = A|B;

assign E = A^B;

assign F = ~A;

Note the use of the "assign". Recent incarnations of Verilog allows flexibility, and for pure

combinatorial logic implemented in an FPGA by using Verilog (that is, not for simulation),

the assign statement is not needed. So the following is equivalent code to what's just above:

wire A;

wire B;

wire C = A & B;

wire D = A | B;

wire E = A ^ B;

wire F = ~A;

or also equivalent:

wire A,B,C,D,E,F;

C = A & B;

D = A | B;

E = A ^ B;

F = ~A;

Now we are ready to write the rest of the code for cname and TOP:

module TOP (

input A, B, C, D,

output reg O);

//

// these are comments just like in c or c++!!!!

//

wire c1, c2;

cname CNAME1(.a(A), .b(B), .F(c1));

cname CNAME2(.a(C), .b(D), .F(c2));

O = c1 & c2;

endmodule

and for cname:

module cname (

input a, b,

ouput F

);

F = a & b;

endmodule

assign F = a & b;

The assign statement tells you that whenever "a" or "b" changes, then assign a new value to "F".

And, even more importantly, if "a" and "b" don't change, don't worry about "F". This is a

common thing in Verilog, that some of the syntax is for simulation, and some for what is called

"synthesis", where you turn logic into real gates.

Mux

A mux in Verilog can be pretty simple. As described above

a mux is something that has 3 inputs - S, D0, D1 - and one output, Q. S controls

which of the 2 inputs D0 or D1 gets sent out onto Q.

In general, the syntax is:

assign out = control ? signal1 : signal0;

where "signal1" is what you want to send to "out" when control=1, and "signal0" when control=0.

So for our mux, lets say that when S=0,

Q=D0, and when S=1, Q=D1. The syntax is:

assign Q = S ? D1 : D0;

Busses

Note that a collection of wires can also be a thought of as a single object called a "bus".

This is analogous to a vector, which is an object that has components.

For instance,

let's say that the input wires A and B are 2 bits of a 2-bit wire we can name (arbitrarily)

as N. Then we can declare N as a 2-bit wire via:

wire [1:0] N;

The syntax [1:0] means that there are 2 bits, and they are

labelled as bit 1 and bit 0. You could also use

wire [0:1] N;

but the former is more common (it comes from

having the most significant bit, MSB, specified before the least significant bit, LSB).

Let's rewrite our code above using busses for both A,B and the results C,D,E,F where

A is the LSB N[0] and B is N[1], and etc for C as the LSB of the bus M:

wire [1:0] N;

wire [3:0] M;

M[0] = N[0] & N[1];

M[1] = N[0] | N[1];

M[2] = N[0] ^ N[1];

M[3] = N[0];

Of course the block of code looks a bit more complex than the one above it, but it's just to

illustrate how busses are used.

Registers

Verilog contains one other type of declaration called registers, declared as "reg".

There are circumstances where reg and wire are interchangable, but basically you use "reg"

when you are referring to flip-flops, latches, etc things that can store a result and

keep it until something changes it.

For most of our purposes, we will use reg to mean flip-flops, which means mostly DFF

primitives. To make a reg you simply do this:

reg F;

How you use it is another story, told next.

Flip-flops

Next we need to know how to describe flip-flops, or DFFs from now on. Any DFF will

need (at the very least) a clock (CLK), and input (D), and an output Q, as shown in

Figure 1. Now go back to what

Verilog was originally invented for - simulation - an imagine you were writing code to

simulate a DFF. You could write the code so that at all times, you check on the value of CLK

and of D, and when CLK transitions, you simulate the action of Q goes to D. But you don't

need to check on D at all times, you only need to check when CLK transitions (from low to high

or high to low depending on what you want). In verilog, we would therefore write the following

code for a DFF (CLK, D, Q) that transitions on the positive edge ("posedge") of the clock CLK:

wire D;

reg Q;

always @ (posedge CLK) Q = D;

That's it, the output Q will be the output of a DFF! Verilog allows you do instantiate as many

DFF as you like, and to save you having to write "always @..." every time, you can do the

following using "begin" and "end":

wire A,B;

reg C,D;

always @ (posedge CLK) begin

C = A;

D = B;

end

There, is, however, a catch concerning the state

Q = D.

To illustrate, what if we have the following code:

wire A;

reg B,C;

always @ (posedge CLK) begin

B = A;

C = B;

end

There are 2 ways to synthesize this into gates. In the first way,

we could assume that the first line,

"B = A", means that we want one DFF where at the

posedge of CLK the output "B" is set to "A", and the second line, "C = B", means that the output

"C" is the same as "A". This is akin to what you would do if writing code for a computer,

and will synthesize to the following:

wire A;

reg B,C;

always @ (posedge CLK) begin

B <= A;

C <= B;

end

Non-blocking is the standard way to instantiate flip-flops, and it is recommended that you

just get in the habit of using <= whenever you are dealing with DFFs inside Verilog

always statements.

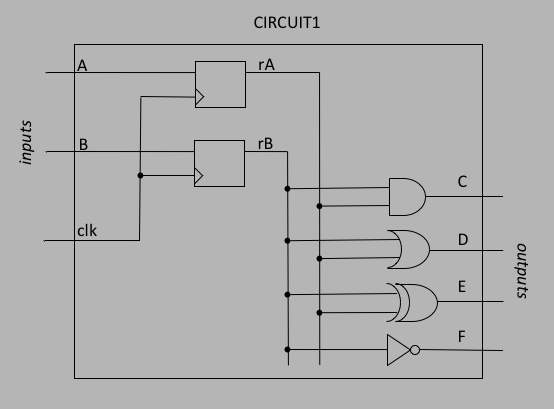

Creating a Real Circuit

module CIRCUIT1(

//

// declare the inputs and outputs

//

input clk,

input A, B,

output C, D, E, F

);

//

// register the inputs

//

reg rA, rB;

always @ (posedge clk) begin

rA <= A;

rB <= B;

end

//

// conbinatorial logic for the outputs

//

assign C = rA & rB;

assign D = rA | rB;

assign E = rA ^ rB;

assign F = ~rB;

//

// done!

//

endmodule

Note that you have to use the "assign" statement for the outputs.

Verilog FSM

module TRAFFIC(

input clk,

output reg red,

output reg green,

output reg yellow

);

endmodule

Note that the outputs are all registers. This is because we will have them change state

inside the FSM, so we might as well make them registers since we will want to register the

outputs anyway (as a matter of good form).

reg [15:0] red_timer;

reg [15:0] green_timer;

reg [11:0] yellow_timer;

In our FSM above, we need 3 lines that signal the timers are done for each light:

These can be wires because they will only denote the condition for the timers to be done,

which will be:

wire R_done = (red_timer == 0);

wire G_done = (green_timer == 0);

wire Y_done = (yellow_timer == 0);

Note that these wires are logic levels, and you can think of them as "true" or "false".

The "true" condition here is that the red_timer counts all the way down to 0, so we

use the syntax "red_timer == 0". Note the 2 "==" signs, this is done to distinguish it

from the assignment "red_timer = 0", which would be a syntax error since

we do not assign values to a reg outside of an always block like this.

always @ (posedge clk)

if (red) red_timer <= red_timer - 1;

else red_timer <= 16'hFFFF;

Things to notice here:

As a shortcut, we could implement all 3 timers in the same "always" block like this:

always @ (posedge clk) begin

if (red) red_timer <= red_timer - 1;

else red_timer <= 'hFFFF;

if (green) green_timer <= green_timer - 1;

else green_timer <= 'hFFFF;

if (yellow) yellow_timer <= yellow_timer - 1;

else yellow_timer <= 'hFFF;

end

A few things to notice here:

Now that we have the timers taken care of, all we need to do now is

specify the FSM. We will have 3 states (RED, GREEN, YELLOW), so we need

a 2-bit register to hold the state value, and we will use that

register, and the R_done, G_done, and Y_done lines to control the state,

which controls the red, green, and yellow registers that control the

lights and the timer. The code looks like this:

reg [1:0] state;

parameter [1:0] RED=0, GREEN=1, YELLOW=2;

always @ (posedge clk)

case (state)

RED: begin

red <= 1;

green <= 0;

yellow <= 0;

if (R_done) state <= GREEN;

else state <= RED;

end

GREEN: begin

red <= 0;

green <= 1;

yellow <= 0;

if (G_done) state <= YELLOW;

else state <= GREEN;

end

YELLOW: begin

red <= 0;

green <= 0;

yellow <= 1;

if (Y_done) state <= RED;

else state <= YELLOW

end

endcase

Things to note:

Putting this altogether, the code will look like this:

module TRAFFIC(

input clk, reset,

output reg red,

output reg green,

output reg yellow,

output reg illegal

);

//

// define the timers

//

reg [15:0] red_timer;

reg [15:0] green_timer;

reg [11:0] yellow_timer;

//

// define the timer "done" lines

//

wire R_done = (red_timer == 0);

wire G_done = (green_timer == 0);

wire Y_done = (yellow_timer == 0);

//

// make the timers

always @ (posedge clk) begin

if (red) red_timer <= red_timer - 1;

else red_timer = 'hFFFF;

if (green) green_timer <= green_timer - 1;

else green_timer = 'hFFFF;

if (yellow) yellow_timer <= yellow_timer - 1;

else yellow_timer = 'hFFF;

end

//

// now comes the finite state machine!

//

reg [1:0] state;

parameter [1:0] RED=0, GREEN=1, YELLOW=2, ILLEGAL=3;

always @ (posedge clk)

case (state)

RED: begin

illegal <= 0;

red <= 1;

green <= 0;

yellow <= 0;

if (R_done) state <= GREEN;

else state <= RED;

end

GREEN: begin

red <= 0;

green <= 1;

yellow <= 0;

if (G_done) state <= YELLOW;

else state <= GREEN;

end

YELLOW: begin

red <= 0;

green <= 0;

yellow <= 1;

if (Y_done) state <= RED;

else state <= YELLOW;

end

ILLEGAL: begin

//

// this is the illegal state! turn on the

// red light and wait for the reset to go high

//

illegal <= 1;

red <= 1;

green <= 0;

yellow <= 0;

if (reset) state <= RED;

else state <= ILLEGAL;

end

endcase

endmodule

Note that we have the "ILLEGAL" state defined. If the FSM gets into this

state, it turns on the red light and turns off the other lights, and waits

for the reset. The state will sit there in ILLEGAL forever until the

reset is asserted. This might not be so great since it means someone (or

something) has to intervene. So, we could easily invent another output,

called "illegal", and have that output asserted

(illegal <=1) when we are in the ILLEGAL

state, so that maybe it will turn on an alarm in some control

room somewhere (or wake up some AI!). Once the reset is asserted,

we have to set illegal <= 0, and transition back into the RED

state and everything should go back to normal.

Xilinx Vivado 2017.2 Introduction

`timescale 1ns / 1ps

In Verilog, the backwards apostrophy "`" denotes a "directive", used

for things like include files, etc. The "timescale" directive

is used to denote the time scale for the simulation, and the

precision. The timescale here is 1ns (the "precision" is 1ps), and

the way that is used is that in the stimulus, if you want to specify

a delay, then if you say "#22" then that means 22ns. The precision

is for the simulator and represents the smallest time you can see

on the waveform. 1ps is pretty precise, and unless you know that

you can simulate things to that level, you should probably change

the precision to 1ns just to save simulation time. But you can also

leave the timescale at "1ns/1ps" and all will be well.

Verilog Testbench

reg clk_in;

reg reset_in;

wire red_out, green_out, yellow_out;

wire illegal_out;

TRAFFIC my_traffic(

.clk(clk_in),

.reset(reset_in),

.red(red_out),

.green(green_out),

.yellow(yellow_out),

.illegal(illegal_out)

)

Paste that code into the file, and

if there are no typo's, it should look like this:

`timescale 1us/1ns

We specify the transitions on the clk_in line by adding the

the following code:

parameter PERIOD = 1000.0;

always begin

clk_in = 1'b0;

#(PERIOD/2) clk_in = 1'b1;

#(PERIOD/2);

end

Notes on the above:

initial begin

reset_in = 0;

end

The Verilog "initial" statement

does just that, initializes things. Since we

set it to 0 and don't change it, it will stay at 0. We of course

do not have the ability with just this code to service a transition

to the ILLEGAL state, but that's ok for now since we don't have the

ability to enter the ILLEGAL state with the stimulus.

always @ (posedge clk)

if (reset) ....

else ....

For asynchronous, it's a bit different:

always @ (posedge clk or posedge reset)

if (reset) ...

else ...

The "or posedge reset" means just that - wait for a posedge of the clock,

OR reset.

initial begin

reset_in = 0;

#100 reset_in = 1;

#100 reset_in = 0;

end

This toggles reset_in from 0 to 1 after 100 "ticks" (here microseconds),

and back after another 100.

So for instance, the code in the TRAFFIC.v

file should be changed to:

always @ (posedge clk) begin

if (red) red_timer <= red_timer - 1;

else red_timer = 'hFFFF;

if (green) green_timer <= green_timer - 1;

else green_timer = 'hFFFF;

if (yellow) yellow_timer <= yellow_timer - 1;

else yellow_timer = 'hFFF;

end

we can add the following 5 lines:

always @ (posedge clk or posedge reset) begin

if (reset) begin

red_timer <= 'hFFFF;

green_timer <= 'hFFFF;

yellow_timer <= 'hFFFF;

end

if (red) red_timer <= red_timer - 1;

else red_timer = 'hFFFF;

if (green) green_timer <= green_timer - 1;

else green_timer = 'hFFFF;

if (yellow) yellow_timer <= yellow_timer - 1;

else yellow_timer = 'hFFF;

end

You can do the same for the state:

always @ (posedge clk)

case (state)

changes to:

always @ (posedge clk or posedge reset)

if (reset) state <= RED;

else case (state)

Now rerun the simulation (it will ask you if you want to discard the old

one, which is ok to do). The problem is sometimes flakey, so you might have

to click on the "quick access" and rerun the waveforms, but after messing

around you should see something like this:

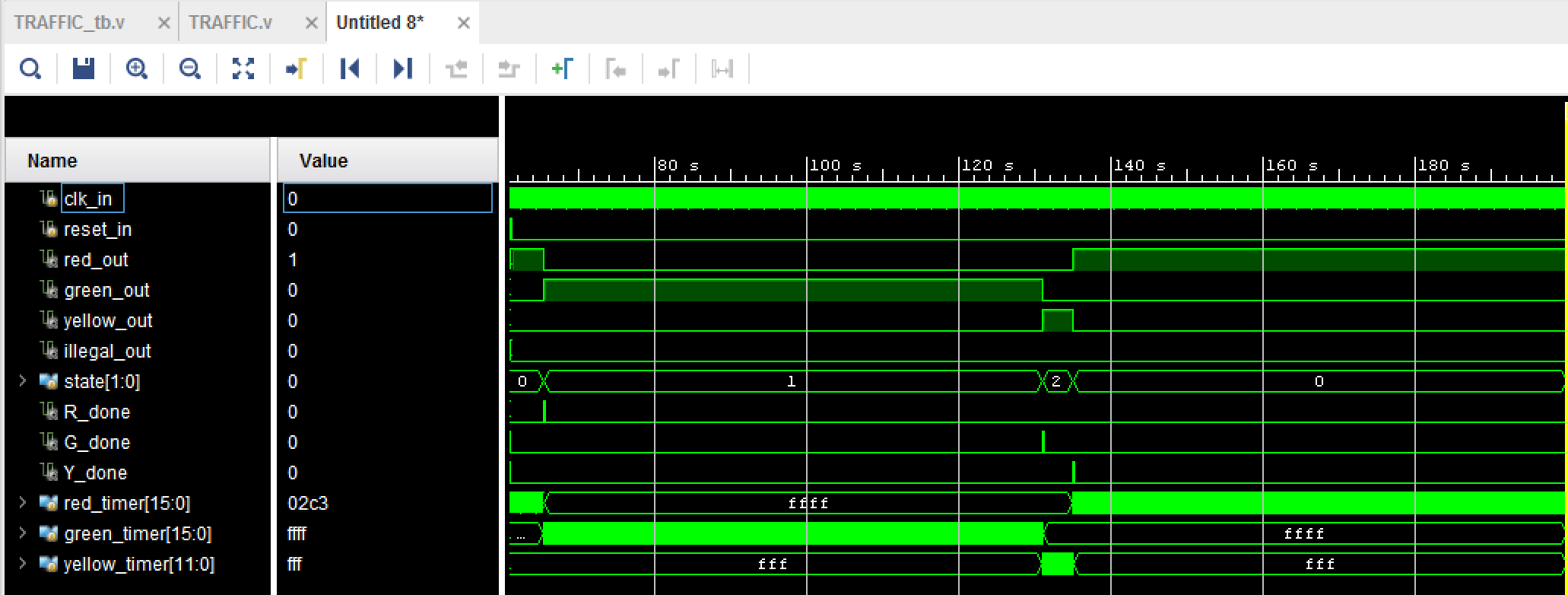

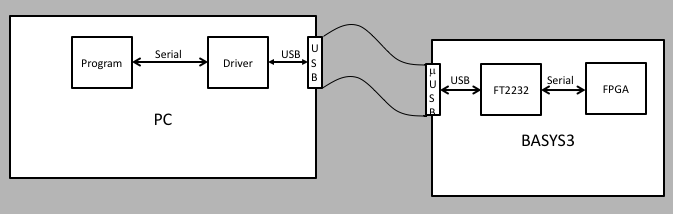

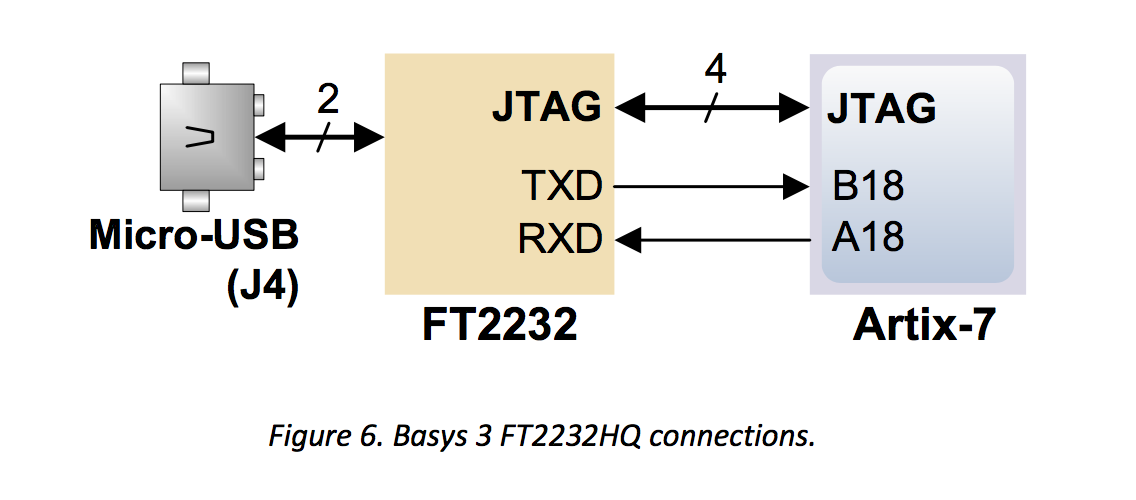

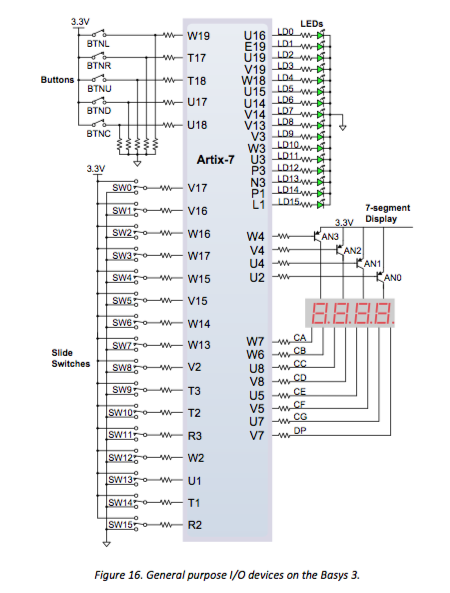

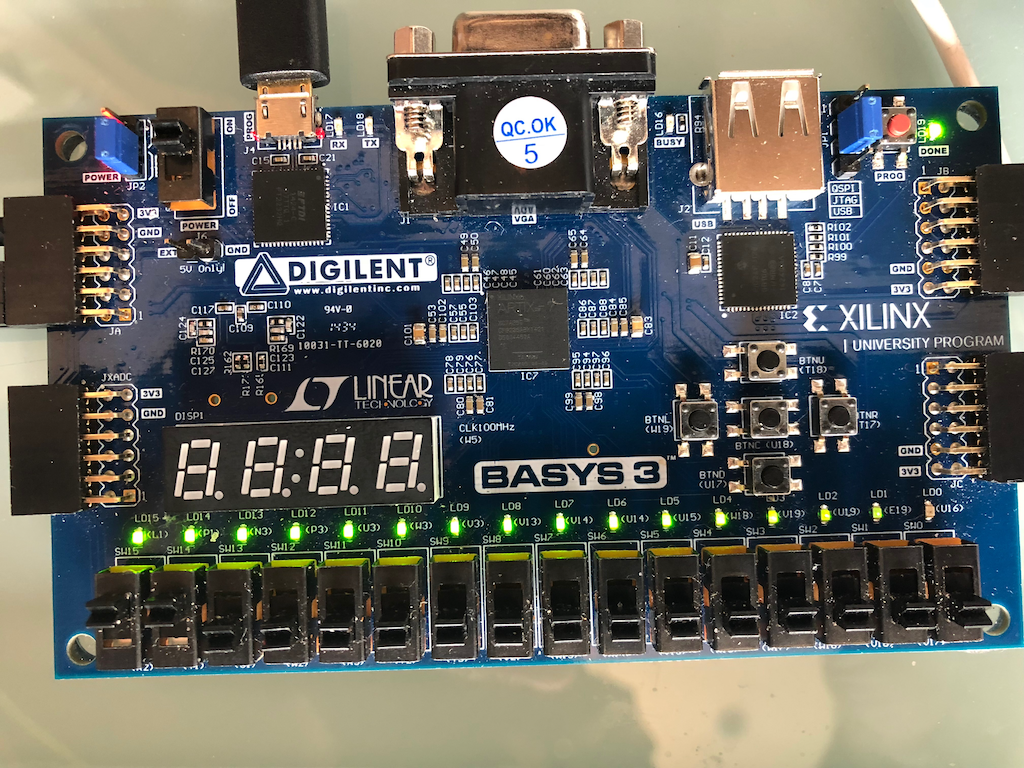

Digilent BASYS 3 Development Kit | Back to top |

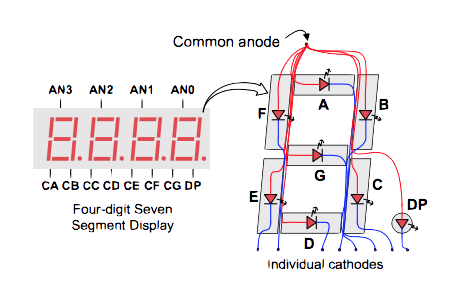

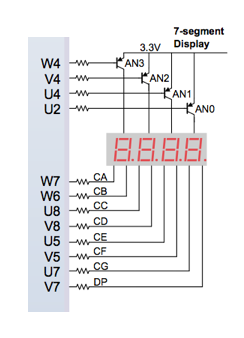

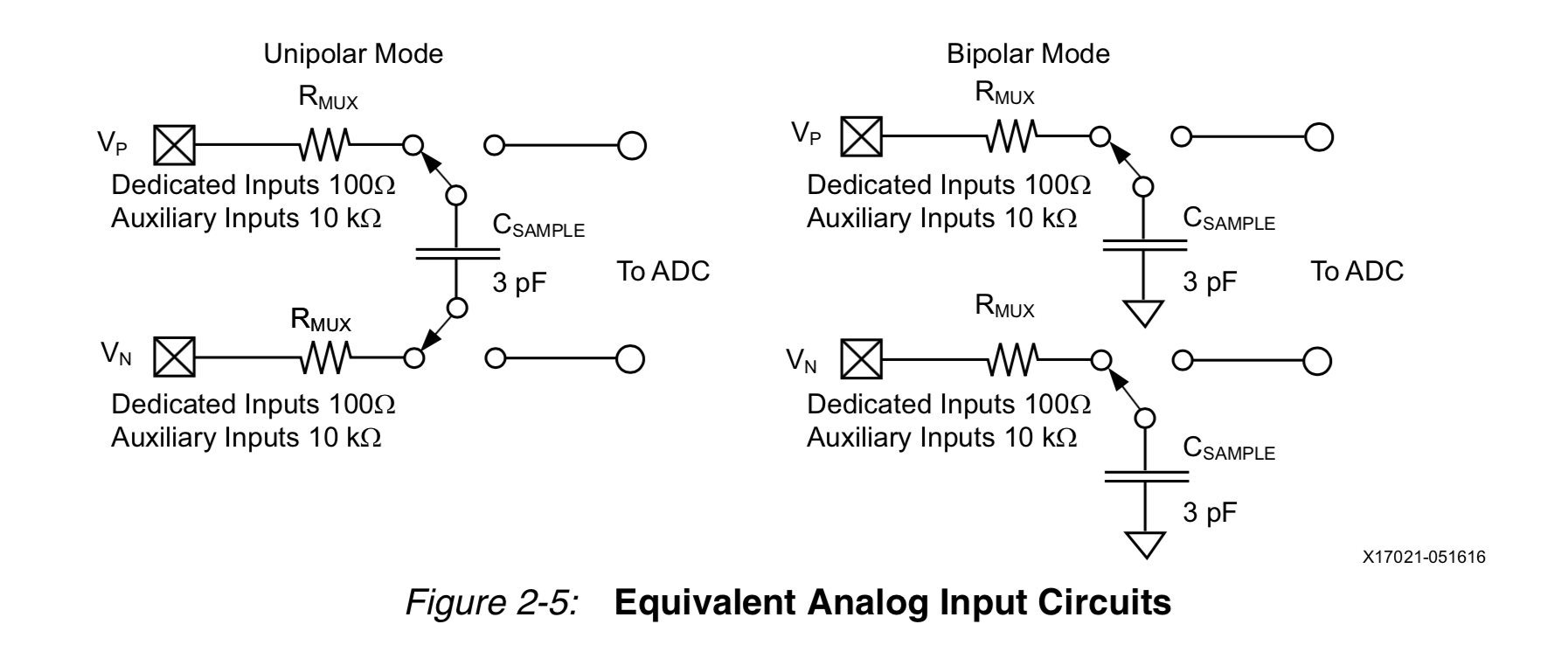

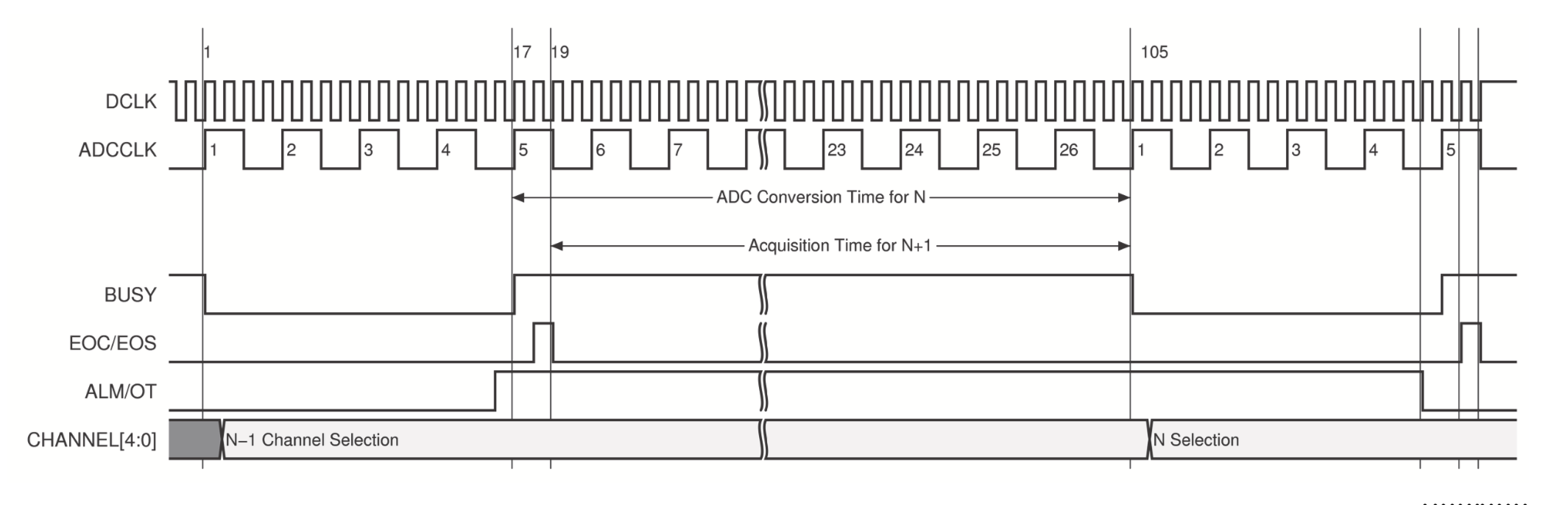

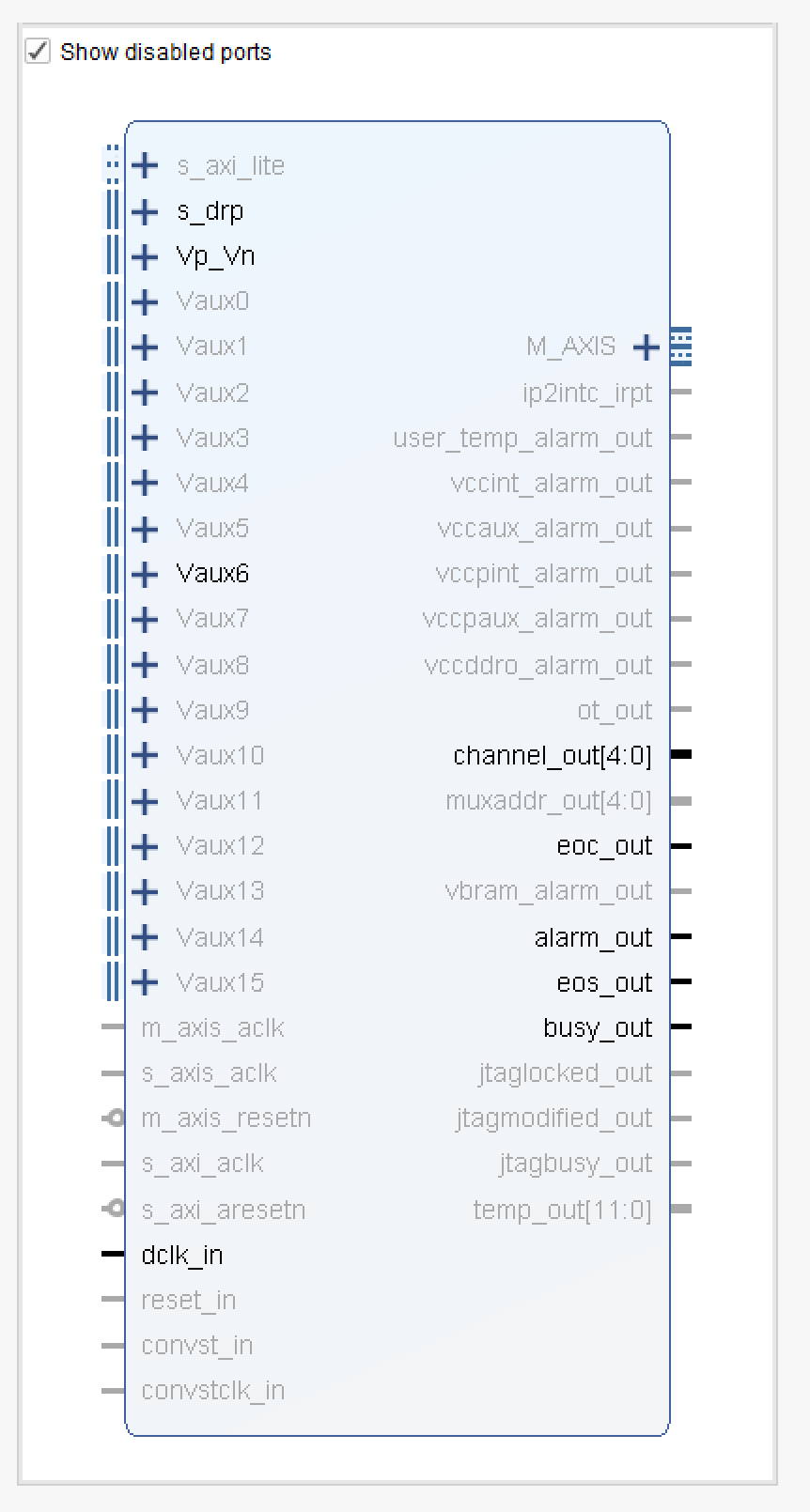

The board consists of a Xilinx Artix-7 FPGA, which has 1.8Mbits of fast block RAM, clock management with PLLs, an on-chip ADC, and can run at up to 450MHz clock speeds.

The board has a VGA connector, 2 types of USB (micro and regular), 5 push buttons, 16 LEDs and 16 switches, and a 4-digit digital LED display. For IO it has 4 "Pmod" connectors, 3 of which are for general IO and 1 has the ADC. It's not a particular powerful board, but is good for learning, and doing simple operations. And once you learn this board, learning more complex ones is easy.

To start, go to the above Digilent web site, click on "Reference Manual", and then click on "Download This Reference Manual". Or you can get it directly from here. That should bring over the file "basys3_rm.pdf", which will become a valuable reference.

There are many other files available on the Digilent web site, with demo projects that you might want to look at once you finish with this tutorial.

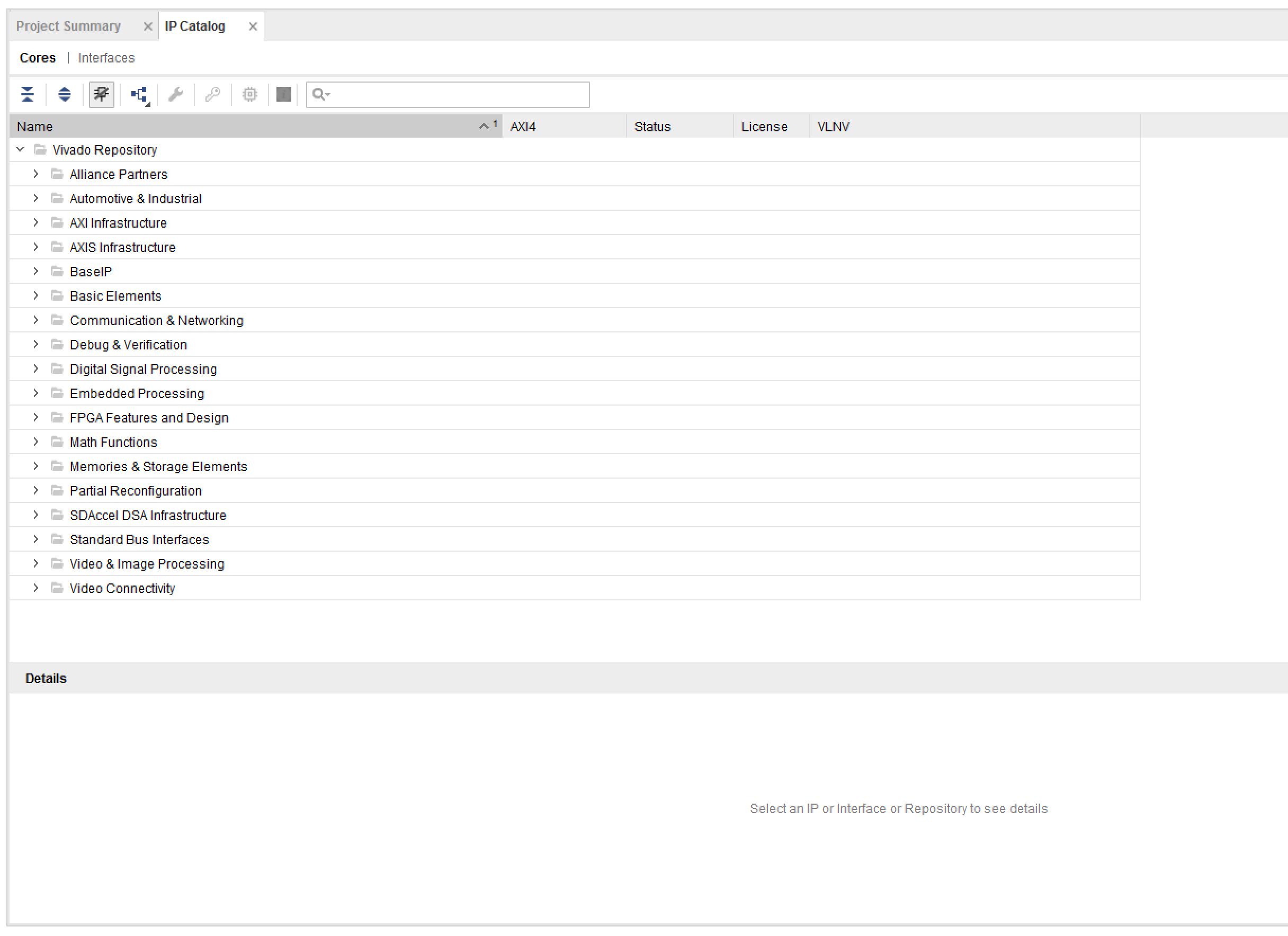

The way boards like this work is that the various gadgets (switches, LEDs, etc) are all connected to specific IO pins on the FPGA. Your first project teaches you how to write Verilog code, synthesize it, then have Vivado do what is called "place-and-route" (P&R), and finally download into the chip. Synthesize specifies the logic, what's connected to what, and P&R determines what actual resources will be used and connected. You have to feed Vivado the source code, and the specifics on the IO pins, and it will do the rest.

The first thing we will do is to build a project that sets up a clock

and counters to blink some of the LEDs. Runing Vivado 2017.2, you should see the

same picture as described above. Click on

"Create Project", and go through the "New Project" wizard, and specify a

new project which you can call "blinking". This will be a "RTL Project",

check "do not specify sources at this time", and that will get you to the

"Default Part" menu. Now we have to specify the exact FPGA part we are

using. You can find this in the "basys3_rm.pdf" file on the first page:

XC7A35T-1CPG236C: "XC7A" means Artix-7 model, 35T is the specific

part (the Artix-7 comes in many sizes), the "-1" is a mistake

(it should be at the end of the model, it's the speed designation)

and CPG236 is the "form factor" (this determines how it's attached to the

board). So you should choose "xc7a35tcpg236-1" in the "Default Part"

window and hit "next", and then hit finish. You will get a fresh window

with nothing in it, like what is shown below:

Click on the "+" in the "Sources" panel, "Add or create design sources",

"Create File", call it "TOP", hit "OK", and then "Finish". It will

next ask you to specify IO Ports, just hit OK there and answer "Yes" to

the next question. It will then show you the file "TOP.v" under the

"Design Sources(1)" item in the "Sources" panel.

Double click on "TOP (TOP.v)" and edit the source file. It will empty

except for the `timescale 1ns/1ps directive at the top, some comments

that you can erase or leave, and the module declaration:

We want to blink the LEDs so we can see them. We will do this by defining

a counter, and tieing each LED to one of the counter bits.

Let's say that the slowest LED will blink at around once every 5 seconds,

or 0.2Hz.

Each subsequent LED will blink x2 faster, which gives 0.4Hz, 0.8Hz, 1.6Hz,

etc. 16 bits is quite a large dynamic range, so some of the faster LEDs

probably won't be seen as blinking, but that's ok for a first project.

For a 100MHz clock, each "tick" is 10ns, so we will need $10^8$ ticks to

get something that ticks every 1 second. If we want a tick every 5

seconds, we want something like $4\times 10^8$ ticks, so we want to solve

the equation $2^N=4\times 10^8$, which comes out to $N=28.6". This says

we need a 29-bit counter. So the code will look like this:

Now you are ready to check if the syntax is correct. If you click on

"Run Synthesis" in the left most "Flow Navigator" panel, it will run the

actual synthesis and report any errors. It will first ask you which

"run" you want to launch, just hit "OK" at that first question. You should

see "Running synth_design" with a circling progress indicator

in the upper right hand corner of the window. If everything worked ok,

it should say "Synthesis Complete" with a green check mark, and come up with

a "Synthesis Completed" pop-up window asking you want you want to do next.

Just hit "Cancel" there.

Next we want to specify the IO pins that the code will use for the inputs

and outputs. To do this you first have to find out what pins on the FPGA

they are connected to. For the clock, section 4 of basys3_rm.pdf (page 6)

tells you it is pin "W5". For the reset, let's use one of the push buttons,

which are specified in section 8 ("Basic I/O"), at the top of page 15. If you

look closely at the board, you will see each of the buttons has a label. Of

the 5 buttons, there are "BTNL", "BTNU", "BTNR", "BTND", and "BTNC" for

left, up, right, down, and center. Let's use the upper one, "BTNU", which on

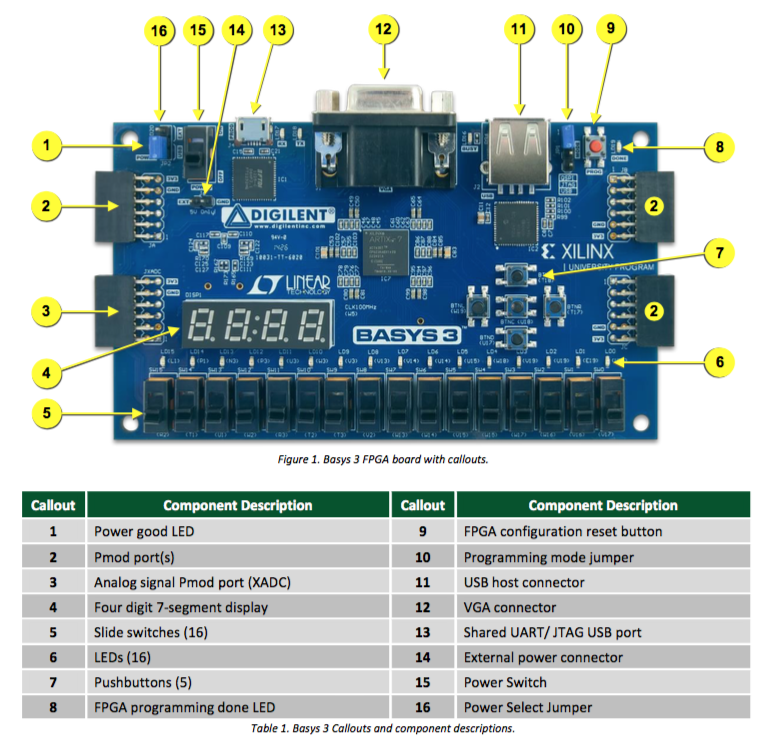

page 15 is at pin T18. Also on page 15 it shows the 16 LED pins (from MSB

to LSB) as L1, P1, N3, P3, U3, W3, V3, V13, V14, U14, U15, V18, V19, U19,

E19, U16. Notice also that the circle shows each LED connected to the FPGA

through a resistor on one side, and ground on the other. This means that

when the FPGA signal is 1, the LED will turn on.

Now we have to set up the source file that specifies the IO pins. This file

is special, and plays a key role in the project. To make it, go back to

the "Sources" panel and click the "+" sign again. In the "Add Sources"

window, change the radio button to "Add or create constraints" and hit "Next",

then click "Create File", give it a name (might as well use the same name,

"TOP"), and click "Finish". Now you have to edit it. In the "Sources"

panel, you should see "> Constraints (1)", click on the ">" and it should expand

and you should see "TOP.xdc". That's the file you want to edit. Double click,

taking you into an empty file.

The syntax is a bit obscure, but the good thing is that once you get it correct

once, you never have to change it! The thing to understand is that you have

to match the pin (e.g. "W5" for the clock) to the IO name in your source (here

it's "clock"). So to do this, type the following:

Next do the same thing for the reset line, and the 16 LEDs. It should

look like this:

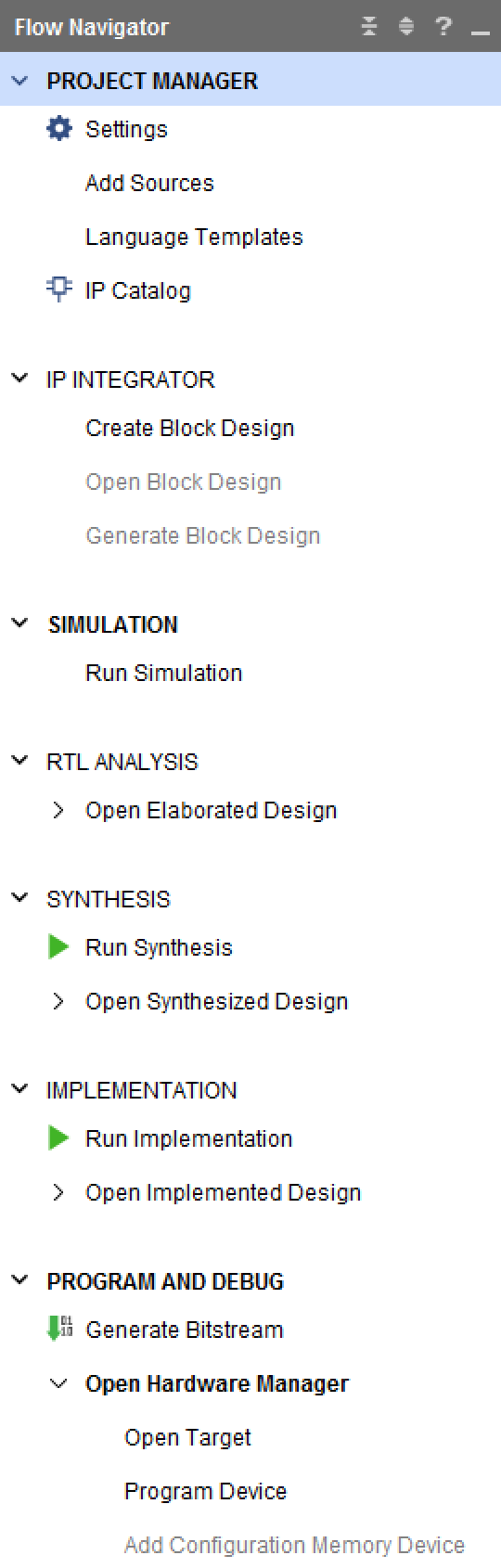

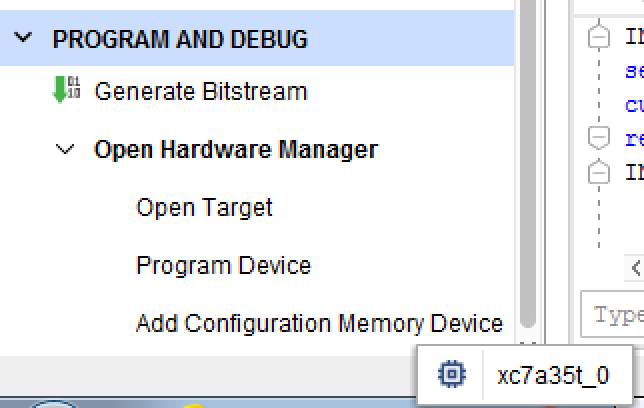

Now you are ready to build it. On the left, in the "Project Manager"

panel, you will see "IP INTEGRATOR", "SIMULATION", "SYNTHESIS",

"IMPLEMENTATION", and "PROGRAM AND DEBUG". Under them are the

operations you can click on. If you click on "Generate Bitstream"

under "PROGRAM AND DEBUG", it will realize that you've not

run the synthesis or implementation stage, and will ask you if

you want to do that by putting up a pop-up window that will say

something about how the "Synthesis if out-of-date" and ask if you

want to run both synthesis and implementation. Say "Yes", and

it will probably put up another window called "Launch Runs". Say

"OK" to that one as well. It will then run the synthesizer,

followed by the place-and-route, if there are no errors, and

then it will make the "bit file". This is a file that can be

downloaded to the FPGA over USB.

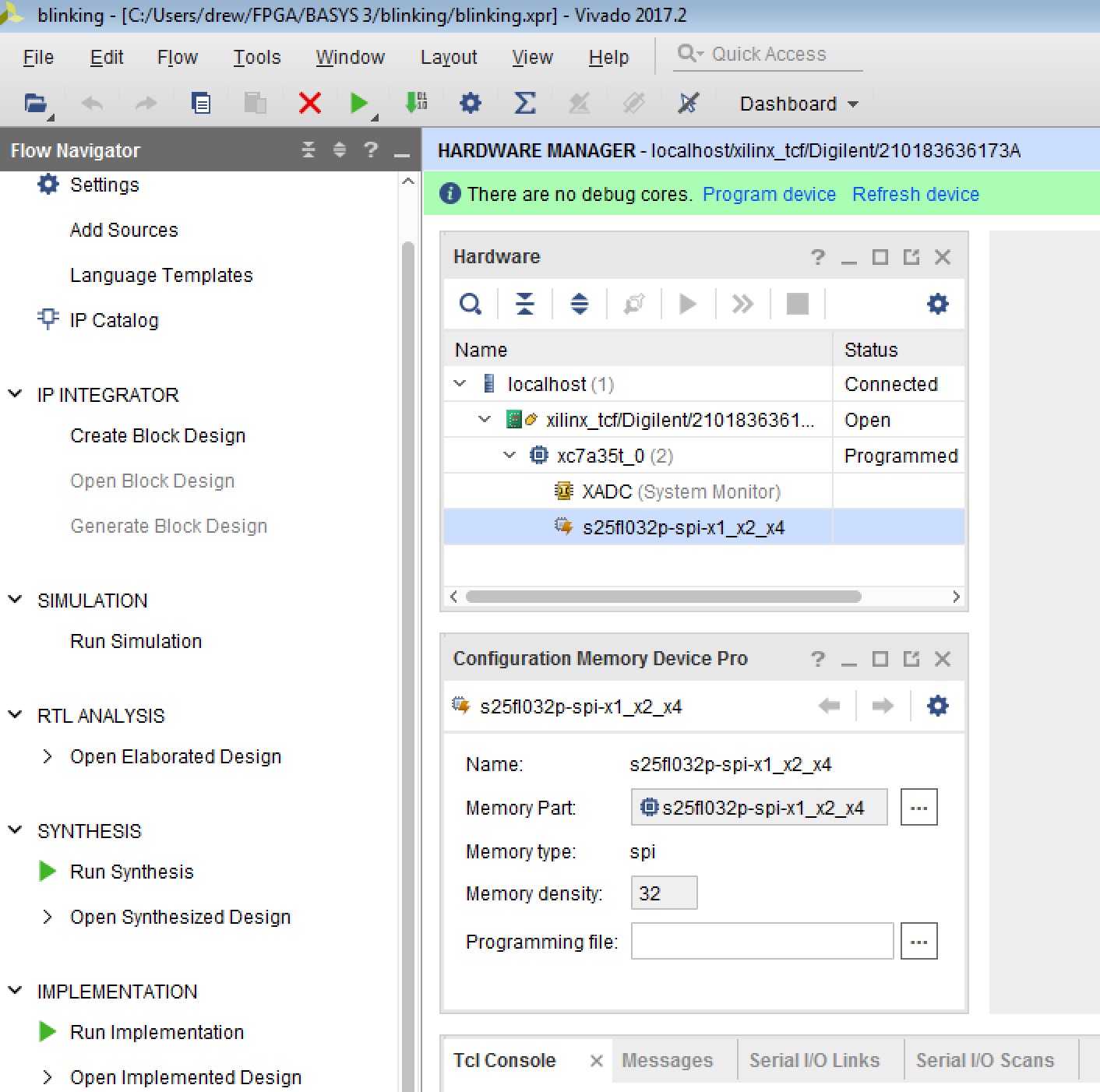

Now go back to the documentation basys3_rm.pdf, and look in section

2 "FPGA Configuration". It details 3 ways to program the board:

using a serial protocol called "JTAG", storing a file in the SPI

flash chip, or transferring from a USB memory stick. We want to

connect our FPGA to our computer using the USB connection, and

program using JTAG. To do this, look for the 4-pin jumper to the right

of the USB connector (upper right when holding the board so that

the VGA connector is on the upper side) called JP1. It will have

4 pins and a blue jumper. You want to make sure the blue jumper

is connecting the middle 2 pins together.

Next, to make sure that the USB will work, you have to look for

the 3-pin jumper JP2 and set it to "USB". This will tell the board

to draw its power from the USB connection, and you have to make sure

that you are using the microUSB connector right next to the on/off

switch. Now you are ready to connect the board to your computer

via USB.

Back to Vivado, if all is well you should see a popup window called

"Bitstream Generation Completed". It wants to know what you want

to do next. Check "Open Hardware Manager" and hit OK. That will

open up the "Open Hardware Manager" tab on the left panel, and under

it you should see "Open Target". Click on that and click on "Auto Connect"

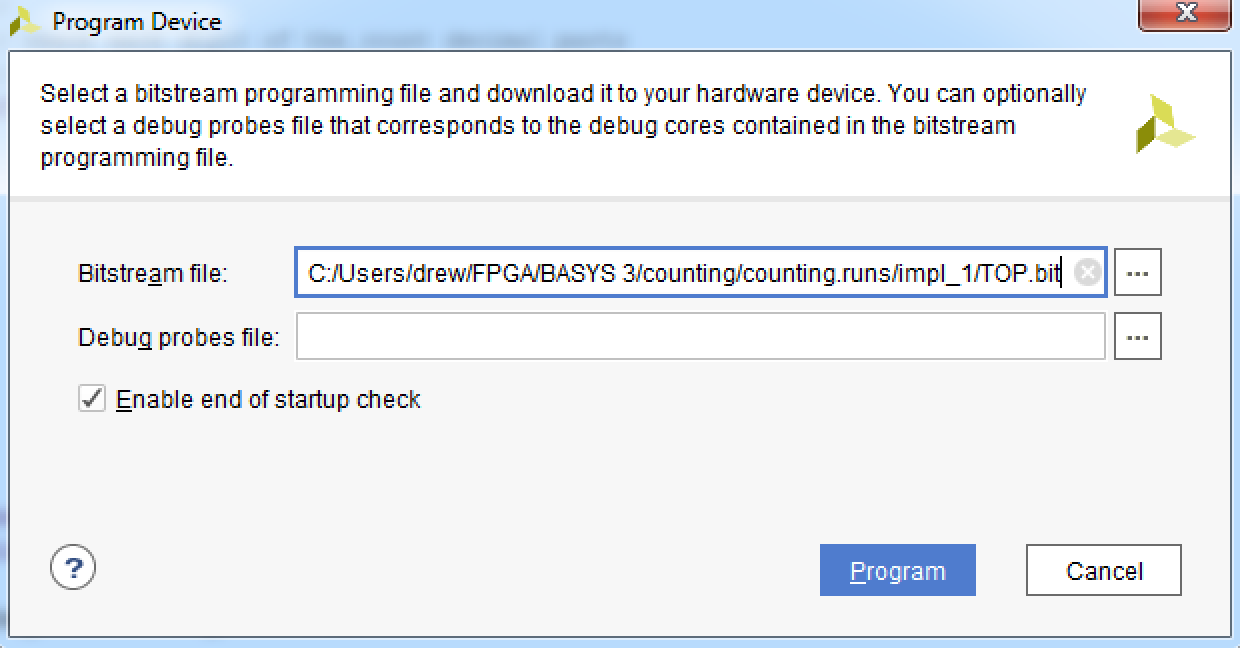

when you see that option. If all goes well, the "Program Device"

option should now be clickable. When you click on that, it will tell

you the devices you can program, which should be your xc7a35t chip.

Click on that. It will bring up a window with the name of the bitstream

file you made. Click on "Program", and if all goes well you should

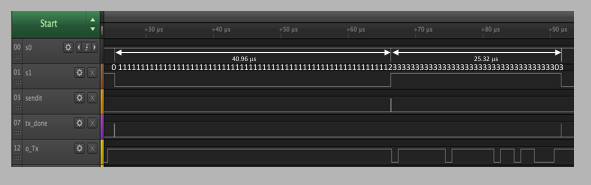

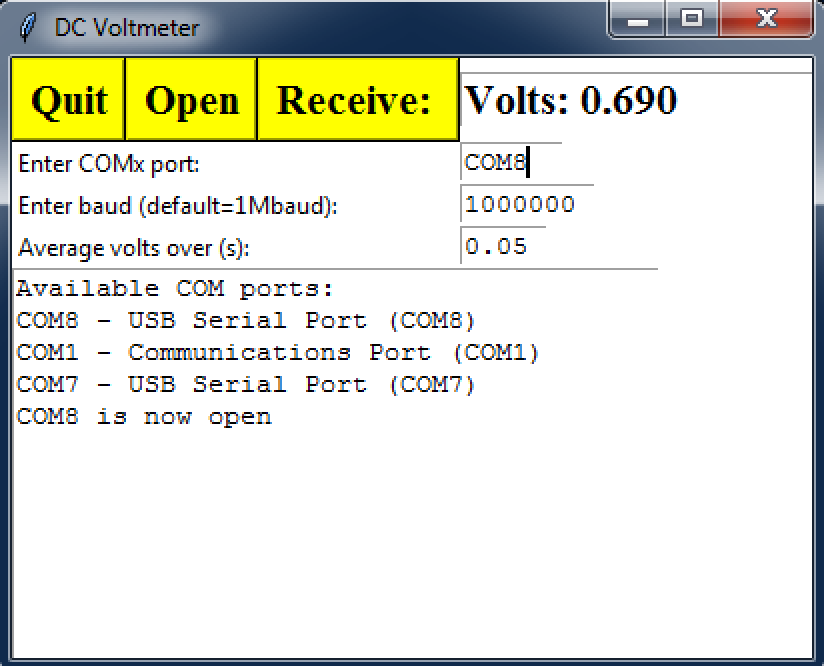

see a window with a green progress bar. After that, the FPGA will be